# Reconfigurable Network Systems and Software-Defined Networking

This paper reviews the current state of the art in reconfigurable network systems, covering hardware reconfiguration and its interplay with software-defined networking (SDN).

By Noa Zilberman, Senior Member IEEE, Philip M. Watts, Member IEEE, Charalampos Rotsos, Member IEEE, and Andrew W. Moore, Member IEEE

ABSTRACT | Modern high-speed networks have evolved from relatively static networks to highly adaptive networks facilitating dynamic reconfiguration. This evolution has influenced all levels of network design and management, introducing increased programmability and configuration flexibility. This influence has extended from the lowest level of physical hardware interfaces to the highest level of network management by software. A key representative of this evolution is the emergence of software-defined networking (SDN). In this paper, we review the current state of the art in reconfigurable network systems, covering hardware reconfiguration, SDN, and the interplay between them. We take a top-down approach, starting with a tutorial on software-defined networks. We then continue to discuss programming languages as the linking element between different levels of software and hardware in the network. We review electronic switching systems, highlighting programmability and reconfiguration aspects, and describe the trends in reconfigurable network elements. Finally, we

describe the state of the art in the integration of photonic transceiver and switching elements with electronic technologies, and consider the implications for SDN and reconfigurable network systems.

KEYWORDS | Field-programmable gate array (FPGA); reconfigurable devices; software-defined networks; switching fabrics

#### I. INTRODUCTION

The Internet provides the infrastructure upon which our modern world is built. Computer networks underpin modern commerce and industry as well as enable the social networks that are at the heart of modern life. They are characterized by a continuous evolution, with tensions between the practical and the desirable. As a flourishing and fertile networking environment, the Internet has required innovative design and management practices to evolve. Into this environment, software-defined networks have come to describe a paradigm for exploring innovation in network design and operation. While software-defined networking (SDN) seems to have appeared suddenly, it is actually part of a long history of trying to make computer networks more programmable and to capitalize on the reconfigurability of the underlying systems.

It is our contention for this paper that SDN and its predecessors are distinctive from reconfigurable networks yet serve to drive the evolution of reconfigurable network systems. We maintain that the approach of the SDN paradigm will dominate the entire breadth of network system reconfigurability: from the configuration of devices at setup to the reconfiguration and update of those devices over their lifetime. The SDN paradigm can offer well-defined

Manuscript received August 15, 2014; revised February 16, 2015 and April 27, 2015; accepted May 12, 2015. Date of publication June 11, 2015; date of current version June 18, 2015. This work was jointly supported by the U.K. Engineering and Physical Sciences Research Council (EPSRC) under Internet Project EP/H040536/1 and by the Defense Advanced Research Projects Agency (DARPA) and the Air Force Research Laboratory (AFRL) under Contract FA8750-11-C-0249. The work of P. M. Watts was supported by the Engineering and Physical Sciences Research Council (EPSRC) under the Research Fellowship Grant EP/I004157/2. The views, opinions, and findings contained herein are those of the authors and should not be interpreted as representing the official views or policies, either expressed or implied, of DARPA or the U.S. Department of Defense.

N. Zilberman and A. W. Moore are with the University of Cambridge, Cambridge CB3 OFD, U.K. (e-mail: noa.zilberman@cl.cam.ac.uk; andrew.moore@cl.cam.ac.uk).

P. M. Watts is with the University College London, London WC1E 6BT, U.K. (e-mail: philip.watts@ucl.ac.uk).

**C. Rotsos** is with the University of Lancaster, Lancaster LA1 4YW, U.K. (e-mail: c.rotsos@lancaster.ac.uk).

Digital Object Identifier: 10.1109/JPROC.2015.2435732

This work is licensed under a Creative Commons Attribution 3.0 License. For more information, see http://creativecommons.org/licenses/by/3.0/

interfaces to devices. While such SDN interfaces may offer a subset of the devices' capabilities, they permit a flexible reconfiguration of network systems independently of the details of the device implementation. As network systems become more complex both in routine operation and in their configurations, SDN provides an evolvable pathway between devices.

To understand the symbiotic relationship between SDN and reconfigurable network systems, this paper takes a top-down approach. We begin with a short tutorial on software-defined networking. A discussion of the interfaces between different elements of a software-defined network follows, and Section III surveys programming languages used across these interfaces. We consider how SDN affected the evolution of programming languages over time, and extend the discussion to proprietary environments. Section IV provides a hardware perspective to reconfiguration in current electronic switching devices. This section describes header processing (as the main operation affected by SDN), and extends to additional networking functions as a place for future innovation in SDN. The technologies for reconfigurable network systems are introduced in Section V, and we predict the impact of these technologies upon such systems. Finally, Section VI considers the integration of photonic transceiver and switching elements with electronic technologies in future systems and discusses the implications for SDN and reconfigurable network systems. We appreciate that this paper targets a wide audience, and therefore suggest that SDN experts skip the remainder of this section along with Sections II and III.

#### A. Foundations of SDN

SDN is a network paradigm. As SDN is an assembly of ideas drawn from a range of innovation efforts, it has several slightly different definitions (e.g., [1]–[4]). Key to all these definitions are the strong isolation between different planes in the network (primarily between the control and data plane, as we explain next), central management, and a high level of programmability. The isolation between control plane and data plane is not unique to SDN; the accumulation of related functionality into layers is common practice across networking disciplines. The strength of isolation has varied across different types of networks.

In order to explain SDN, let us consider the common current network environment, the Internet. At its heart, the Internet consists of routers connected with each other and with hosts, servers, and clients. Routers form the nodes of a network interconnecting multiple hosts and other routers. Each router forwards packets along links, and the router decides where to forward packets in the data plane using information derived by the control plane. A simple control plane is a computer program that (among other duties) uses routing protocols to discover pathways upon which to forward packets. It had been commonplace for a single manufacturer to provide an integrated system

that would implement a given set of routing protocols, compute appropriate forwarding rules, and install these in the hardware of the data plane. Such systems provide little opportunity to install new or experimental control planes (e.g., a new algorithm that routes packets according to a different criteria) but in return the limited flexibility was balanced by a system that offered most customers what they required. Each router vendor would satisfy the compliance need, meaning their products behaved correctly and conformed with appropriate Internet standards. However, such a vertically integrated system offered little opportunity for innovation. Additionally, the vertically integrated systems meant that a superior data plane from one vendor could not be simply connected to the superior control plane of a competitor vendor.

Such vertically integrated systems meant that network service providers (and researchers) were frustrated by the time and expertise needed to develop and deploy new network services. The widespread use of vertically integrated networking equipment has left limited opportunity for innovation. Aside from customers and researchers that wished to deploy and reinvent the control plane, researchers focused upon the network data plane realized that commercial systems rarely provided the right environment to evaluate their ideas. In contrast to the software used for implementing new routing algorithms in the control plane, innovation in the data plane could require measurements, and redesigned control of the data plane's high-speed networking hardware. Given that data-plane design is a delicate balance of considerations (speed, features, and pricing), unnecessary features were shunned by commodity network-equipment vendors. This lack of opportunity for innovation motivated the development of SDN on reconfigurable systems.

#### **B.** Reconfigurable Systems

The reconfiguration of hardware has been a core requirement underlying many decades of networking success. Reconfiguration in network systems covers a wide spectrum of use cases from the onetime configuration of devices when a system starts its life, through the runtime reconfiguration of algorithms implemented in networking devices to allow their operation at line rate, to adapting the operation of previously configured devices by maintenance programming.

Throughout much of the long history of computer networking, reconfigurable logic has provided core functionality in commodity electronics. Such an example is the early use of programmable array logic to permit the programming of unique device identifiers [e.g., media access control (MAC) address] after device manufacture. This permitted the cheap manufacture, assembly, and testing of devices—despite each one being uniquely configured.

Field-programmable gate array (FPGA) devices have a long association with high-speed networking equipment. For example, FPGA devices are commonly used to provide

the control logic required to interconnect application-specific integrated circuit (ASIC) devices while providing management functions along with power and thermal control. FPGA devices have been widely used on highspeed network interfaces to implement rules intended to process incoming and outgoing packets (e.g., for filtering packets) and continue to see use as offload processing, configured to provide data processing as either a coprocessor alongside more general purpose computer systems or a less-flexible dedicated network switch silicon. Since FPGA devices can be configured in live systems, they have seen widespread use implementing network protocols, and protocol-translation services. In each of these cases, the FPGA can be reconfigured as requirements change.

In this paper, we treat reconfiguration as a spectrum of activities ranging from initial configuration, through insystem changes in functional design (complete and partial reconfiguration), to include updating parameters within a reconfigurable device (such as table entries). We distinguish between reconfiguration and programmability. By reconfiguration we refer to selecting one option from a given set (including a range of values, e.g., set register value to 0xF) to change the operation of an element. By programmability, we refer to providing a set of instructions (of varying type, number, and order, e.g., repeat a lookup operation until a match is found) to set the operation of an element.

#### C. Biased History: Reconfigurable Network Systems and SDN

We assert a close relationship between reconfigurable (network) systems and SDN. Recently, SDN owes much of its journey into popular consciousness on the back of OpenFlow [5], an interface between the control plane and the data plane. However, the core ideas of software-defined networking predate that work by several decades. Reconfigurability has played many critical roles, from the earliest implementations of network prototypes [6] through work on active networks [7] and flexible network systems [8]. In addition, a series of SDN interface approaches propose alternative protocols for control-plane programmability, and we present them extensively in Section III.

The OpenFlow interface was first and foremost an open-source standard. The code, documentation, and reference implementation (software and hardware) are openly available to any interested party. Such practice is not new, as much of the early Internet Engineering Task Force (IETF) work began as open development. What makes the OpenFlow particularly interesting was its reliance on open-source hardware based upon reconfigurable systems [9]. If SDN owes much of its relaunch to OpenFlow, then OpenFlow owes much of its popular adoption to the ready availability of implementations. The NetFPGA [10]-[12] platform, itself an open-source FPGAbased reconfigurable platform, provided the ideal base for a prototype OpenFlow hardware implementation [5].

It is clear that reconfigurable systems have made core contributions to networking in general and SDN in particular. Feamster et al. [2] provide a technical history of SDN, and additional surveys can be found in [3] and [13].

#### D. Scope and Related Work

We presume that the reader is familiar with the key elements of common Internet-style packet-switched networks, where each packet has information sufficient for conveyance toward the final destination. However, any network is more than a simple process that forwards packets along links in a network. Networks are subject to a combination of requirements such as the coordination of decisions about where to send packets, the need to optimally interconnect different types of physical networks (e.g., wireless mobile and wired), or the need to subdivide a network based on geography or administrative domain. Each function adds complexity to the organization and operation of the underlying network. Tackling the combinatorial effect of complexity is not specifically considered within the Internet. It is the control of this expansive complexity that SDN attempts to tackle.

We have purposely limited the scope of this paper to local area network (LAN) and wide area network (WAN) applications. While the intersection of reconfigurable systems and SDN is wide ranging, the resurgence of interest in SDN has remained firmly focused upon LAN and WAN (with emphasis on Internet protocols and wired Ethernetbased networks, unless otherwise noted). While this is not an SDN-imposed restriction, it is the most common use case for SDN-based networks.

Similarly, we limit the scope of this paper to wired networks. SDN is independent of the physical media, as the abstraction of the network elements make this implicit. However, we will not explicitly explore the implications for mobile/wireless networks here. Interested readers may find relevant an early SDN-enabled for mobile networks [14], optimizing placement of overlapping LTE cells [15], and an example of a full enterprise deployment incorporating authentication, authorization, and accounting [16]. Additionally, we mention only in passing the plethora of other software-controlled networks, such as advances in networks-on-chip (NoC) reconfiguration under software control. Such work has ranged from reconfigurable topologies [17] and configurable channels [18], to fault recovery [19] and circuit-switched NoCs [20]. Finally, while reconfigurable systems have made an impact upon the wireless domain through software-defined radio (SDR) [21], we will not discuss these technologies here.

While not specifically SDN, as a matter of scope it is important to make clear the relationship with network functions virtualization (NFV). NFV is an emerging network architecture concept that employs host virtualization technologies such as Xen [22] that allow entire classes of network node functions to be treated as building blocks. These blocks may be connected, or (in the language of NFV) chained, together to create communication services. It is clear that SDN complements the NFV idea and provides a powerful enabling tool. However, NFV is a mechanism for organizing elements along the datapath in a network (e.g., firewalls, network intrusion detection systems, caches for various traffic types). Since an initial white paper [23], researchers have extracted some of the ideas of NFV into the form of a reconfigurable network system [24], and there is a nascent community engaged in abstracting such data-plane elements to enable SDN-like innovation in network function control [25].

#### II. SOFTWARE-DEFINED NETWORK

#### A. Introducing the Software-Defined Network

Utilizing SDN, the software-defined network may naively be considered as based upon simple concepts: SDN networks routinely utilize a common and well-defined interface between a control plane and a data plane. The control plane is responsible for global coordination (such as routing and fault recovery). The data plane is where routine packet-by-packet operations occur. Exceptional events in the data plane become events sent to the control plane. The control plane can modify data-plane behavior. The separation of the control plane and the data

plane is not a new concept. It might be argued that what SDN popularized is the use of a clearly defined interface between the two. Next, we compare a traditional router with SDN.

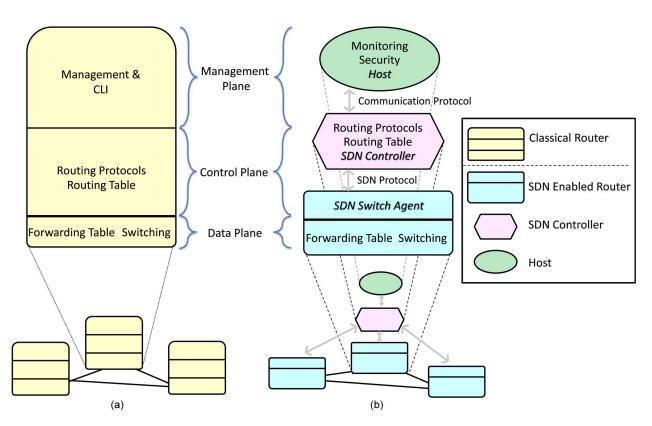

Fig. 1 illustrates a router-based network alongside its SDN equivalent. In each case, there is a subdivision of work between the data plane and the control plane. The data plane implements several processing functions on each packet: 1) buffering (and/or storing) packets while the headers are processed; 2) examining the header and looking up header information in the forwarding table (the table storing the forwarding rules) to identify the actions the switch should perform; and 3) queuing packets for transmission. An example of a switch action is updating the time-to-live (TTL) in IP packets. (The TTL field is decremented each time a packet passes through a router. When the value reaches zero, the packet is discarded and an error is generated.) These functions are done for all routers, whether SDN or not.

In both cases, the control plane must handle all possible circumstances, including any exceptional packets. For example, in IPv4 and IPv6, packets that exceed their TTL require such exceptional handling to include discarding the packet and returning a control packet to the source reporting the error. The control plane also configures the data plane and manages the mechanisms by which the data

Fig. 1. Functionality in a classical router-based network and the equivalent SDN network. (Hosts are not shown.) (a) Classical-router network. (b) SDN network.

plane forwarding tables are computed and configured. Typically, this involves running one or more routing protocols, exchanging local routing information with other router peers, and deriving a local forwarding table.

Commonplace approaches to separate control-plane and data-plane functionality involve implementing controlplane functionality in a high-level programming language and operating on a general purpose processor. The control plane may implement sophisticated programs, but without optimization, per-packet processing performance may be low. In contrast, the data plane implements optimum network performance (e.g., high per-packet processing rate, minimal latency), but only for the most commonly encountered cases.

As show in Fig. 1, equivalent SDN systems support identical functionality. These consist of a data plane with an optimization for high-speed forwarding and a control plane to handle exceptions and create content for the forwarding table of a switch element. The differences arise due to differences in the abstractions defined between the dataplane system and the control-plane system among SDN implementations. Effectively, SDN treats network devices as fast but simplistic forwarding elements which can be used as building blocks for higher order functionality, such as routing and access control. Furthermore, by providing a common abstraction, new architectures can arise. For example, as illustrated in Fig. 1, the SDN network may share a single SDN controller among different switch elements.

#### B. Reducing Complexity: Motivation for SDN

Network architects, engineers, and operators are presented with the challenge to provide state-of-the-art network infrastructure and services, all while minimizing the associated purchase and operation costs. Researchers in networking extend this challenge by also seeking to explore novel and potentially disruptive ideas in a state-ofthe-art network infrastructure. It is into this space that SDN has arisen.

A core design principle of the SDN paradigm is to define an open interface, exposed by network devices, which allows control of the connectivity and traffic flow of the device [26]. This interface definition allows seamless network reconfiguration of the network control logic. Effectively, SDN tries to define a common abstraction which encodes the reconfiguration capabilities of the underlying network devices.

The SDN thesis is in two parts: first, networks lack the ability to enable innovation, and second, they lack proper network abstractions. These limitations have resulted in an inability to keep pace with user requirements and to keep the costs of such networks under control. In part, this challenge to innovation stems from user requirements that are inflexible or unclear (e.g., user requirements that are stated informally, or user requirements that are statically bound to particular systems). Pursuit of the SDN thesis leads to the notion that control and maintenance of network infrastructure and services is better done by a machine which exploits the common control abstraction across all network devices, from programmatic configuration to monitoring and mechanized management.

We now describe examples where the use of SDN makes tangible impact on the complexity of a problem. The first shows how SDN can be used as an innovation enabler. In this case, SDN addresses an ongoing problem. A network operator wishes to try new ideas in an already complex network. The operator wants to understand what changes occur, how those changes have impacted the network, and to understand and interpret the resulting systems. Furthermore, in common with any good science, the operator wants repeatability with well-defined constants and variables—particularly in attempting to quantify the impact of the change. The idea of testing innovation within existing networks provided a core motivation of the original OpenFlow paper [5].

A second motivating example shows how a consolidated viewpoint impacts networking. A consolidated viewpoint is one whereby an observer could see and/or control an entire network rather than rely upon triggering a desired behavior by configuring many autonomous devices. A consolidated viewpoint also permits both improved behavior and new applications. Imagine a security scenario: a malicious machine is interrogating machines, probing for vulnerabilities, but doing so in a nondeterministic way. Observations of small amounts of malicious traffic may go unnoticed. However, centralized information would have identified the malicious intent faster through improved global awareness.

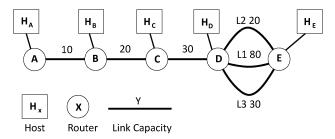

Now we consider a more sophisticated routing example. In a simplified network, all links are interconnected by routers, each making its own local forwarding decisions about the next hop to send a given packet based on destination address. In contrast, routing in such a non-SDN network is the result of a coordinated exchange of information about local connectivity, whereupon a routing mechanism can identify new or updated pathways. In a distributed network of routers, an operational failure leads to each router identifying the optimum path and making simple optimizations leading to local forwarding rules. However, despite a simple routing solution electing an apparent optimum, it is in fact a local minimum, and this solution can lead to overloading in (other) nonlocal links. The solution then involves each participant router iterating solutions in the hopeful (but nonguaranteed) pursuit of a global optimum. With more (nonlocal) routing information, a better global routing solution could be found, avoiding the intermediate local minima and improving convergence. A very simple example of this situation is shown in Fig. 2: Each host ( $H_A$  through  $H_D$ ) communicates with host  $H_E$ , with a link capacity of 10. Initially, all the traffic goes through link L1. In a distributed network, if link L1 fails, each of the routers will autonomously try for the next best path. This means that initially all traffic will

Fig. 2. Simple network topology with multiple links between routers D and E.

be directed to link L2. Suppose A and B succeed. Then C and D will fail, as the link will be overprovisioned. C and D will then autonomously try link L3 and succeed. In a network with centralized traffic management, such as provided over SDN, router D will first announce the failure to the traffic management application, which reprograms (through the controller) all routers.

As suggested by this example, the ability to make routing decisions is improved when a regional or global awareness of a system of routers is available. Without an SDN approach, the use of local-only information leads to poorer results in general and does not take advantage of well-established heuristics that can operate when knowledge and control on a broader scale is possible.

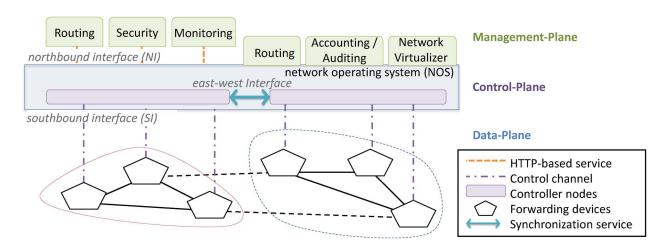

#### C. Actualization of SDN

To date, network complexity has been tackled by modular decomposition or modularization (breaking a problem into subtasks) and abstraction (dealing with ideas and roles rather than specific implementation details). The same principles apply to the use of SDN to limit network control complexity. SDN control functionality is commonly divided into multiple abstraction layers, in an effort to simplify and modularize the control tasks. Fig. 3 presents a generalized model of an SDN-enabled network control architecture. The architecture comprises three distinct layers: the data, control, and management planes.

The data plane, the lowest layer of the architecture, is composed of the hosts and devices of the network. In order to enable programmability by the control plane, the SDN paradigm builds a simple and clean functional separation of network devices, aiming to transform each device into a simplified forwarding engine that can be remotely controlled through a well-defined but restricted southbound interface (SI). The data-plane functionality of an SDN device comprises a limited set of operations, such as packet header parsing and extraction of a header field tuple, support for a fixed set of packet operations (such as header field manipulation and forwarding through a specific set of ports), and the ability to match packet header tuples against a lookup memory primitive (e.g., a hash table or a content addressable memory [27]). By contrast, the control interface of the switch enables an external entity to define the lookup memory entries and associate them with packet actions (e.g., forward any packet addressed to A using the nth port of the switch). Such control functions can also encompass the handling of exception packets, in cases where no specific handling rules exist for a packet, and for the accumulation of usage information such as packet counts. A final essential feature for the SI that shapes the SDN abstraction across layers is the flow-centric treatment of packets. In the context of SDN, a network flow is an ensemble of packets with header values that match specific ranges. For example, a TCP flow can be identified through a match with exact values for the IP addresses, the IP protocol field, and the TCP port numbers,

Fig. 3. Model of an SDN control architecture. Functionality is separated in three layers: the data plane, the control plane, and the management plane. Integration between layers is realized through the southbound interface (SI), connecting network devices with the network operating system, and the northbound interface (NI), connection control application with the network operating system.

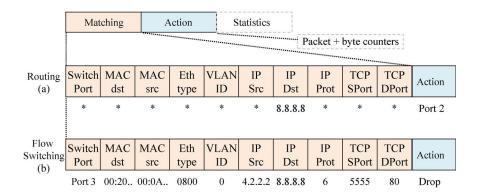

Fig. 4. Examples of matching rules and actions. The first example (a) shows a routing rule matching of a destination IP address 8.8.8.8 to output port 2. The second example (b) shows a rule matching each field in the header with a specific value, and dropping the packet if all the fields are matched.

while a routing flow can be reflected through a match for the IP destination address. Effectively, the flow granularity is user defined and dynamic, comprising any set of packet header fields (Fig. 4 presents the available header fields in OpenFlow version 1.0). The flow abstraction is fundamental across all network devices and permits control convergence across different network elements (e.g., routers, switches, firewalls, and middleboxes).

In order to illustrate the design of a pragmatic SI, we elaborate the abstraction of the OpenFlow protocol. Each network device is modeled as a datapath, an ensemble of device ports and flow tables. The flow table is a core protocol abstraction reflecting the device forwarding policy.

Each flow table entry is split into three sections: the flow match, the action list, and the statistics. The flow match defines a flow using all the important header fields of a packet. Field wildcarding is supported, meaning any value will be accepted on the designated fields. The flow action list contains a list of packet operations, allowing header modifications and packet forwarding, applied to every matching packet. Finally, flow statistics of matched data include both byte counters and packet counters. Fig. 4 presents the structure of the flow table entry and two example entries. The first is a routing flow, matching only the destination address and forwarding packets with destination IP address 8.8.8.8 to port 2. The second is a flow switching entry, where all ten fields need to match the table entry. The action is set to drop a matched packet. We use these examples to highlight the generality of the OpenFlow abstraction to flexibly accommodate data-plane processing complexity. While the routing rule requires only a destination IP address extraction from each packet, the flow switching policy exhibits higher complexity. Because flow matches from different flow entries may overlap, the protocol assigns a flow priority to each flow entry in order to break ties. In addition, each flow entry contains optional timeout values, which identify the time period that a flow remains active in the flow table. Furthermore,

the protocol provides message primitives to control the flow table, to query switch configuration and port and table statistics, and to intercept and inject data-plane traffic. The ability to intercept traffic is commonly used as an exception channel for traffic that is not handled by the device policy and, along with the network statistics polling messages establishes a set of powerful primitives to develop proactive and reactive control schemes.

The primary (operational) benefit of the SDN paradigm is the flexibility to rapidly develop new control logic in networking elements and effectively enable evolvability. In order to achieve this, the SDN paradigm exploits the flexibility of high-level languages and employs a control-plane layer to implement the network logic on general purpose servers. The control layer, often referred to as the network operating system (NOS), provides abstracted interfaces to network forwarding elements of varied capability and SI support, while managing contention for resources. Effectively, the control-plane layer is responsible for synthesizing the output of the control applications running on top of the NOS into a forwarding policy and distributing it to all the switches of the network. Additionally, the control plane is responsible for transforming input from the SI into semantically richer higher level abstractions, e.g., establishing the network topology. Furthermore, in order to improve the scalability and availability of the control plane, existing NOS borrow established techniques from the distributed systems domain to achieve horizontal scaling between control-plane nodes. Such distributed NOS employ an abstraction layer, the east-west interface, which allows seamless synchronization between the views of individual data-plane nodes. Such interfaces are implemented using distributed consensus protocols or popular database services, like the Infispan [28] distributed key/value store which is employed by the OpenDaylight controller [29]. While maintaining a common network view between distinct nodes, this approach permits the data-plane control requirements to be scaled among multiple servers.

There exists a tension between centralization and decentralization. Centralization is considered to offer enhanced network control and planning. For several of the SDN use cases (e.g., security or globally optimal routing), centralization is an enabling force. However, such centralization runs contrary to historic practice. Decentralized approaches are sometimes regarded as more resilient to failure and robust to changes in circumstance. While this tension is not resolved, significant efforts are taken by NOS (e.g., OpenDaylight) to ensure fundamental properties of resilience can be maintained by multiple redundant servers.

Finally, the top layer of the SDN architecture, the management plane, consists of the management applications which manifest the control logic of the network. This layer consists of common network control applications like firewall, access control and routing, but can also enrich the network capabilities by introducing new applications. Interaction between control applications on the management plane and the control plane is realized through the northbound interface (NI) of the NOS. The NI is defined by the control plane of the network. Its primitives vary between platforms, spanning from direct SI access to indirect access based on building new primitives (synthesizing multiple low-level interactions of the SI). Control applications can run on hosts separate from the control-plane nodes, accessing the NI through various standard services, or they can be physically integrated with the control layer during the compilation of the NOS.

## III. PROGRAMMING LANGUAGES AND PLATFORMS FOR SOFTWARE-DEFINED NETWORK RECONFIGURATIONS

The SDN paradigm defines an abstract architectural model for the control of the network and identifies some key design properties (e.g., flow-centric treatment of traffic). The realization of SDN across the different layers of the network still remains an open question for the research community, which we elaborate on in this section.

The majority of research efforts in the field of SDN programming languages and platforms have focused on the control and management planes, while data-plane research, with its line-speed expectations, has limited research to only a few facets based upon reconfigurable devices.

### A. Management Plane, Control Plane, and NI Programming Languages

The management and control plane of the SDN architecture orchestrates the network logic. The primary design goal of the control plane is to expose an application programming interface (API), the NI, which allows developers to focus on programming the network rather than the device, thus abstracting the effort to consolidate control across multiple devices and locations. In addition, control-plane platforms aim to construct new reconfiguration abstractions, by synthesizing low-level reconfiguration capabilities of the

underlying network infrastructure. For example, heterogeneous support of SDN reconfiguration capabilities across the network forwarding devices (e.g., variable support for fastpath packet modifications between forwarding elements) can be abstracted through runtime network policy optimization (e.g., setting up end-to-end paths that apply packet modifications on the most appropriate device of the path).

The NOS is the main building block of the SDN control plane. Similar to a traditional operating system, it executes management-plane applications, and it is responsible for coordinating access and securing network resources. Early NOS approaches, like Ethane [30] and NOX [31], provided low-level OpenFlow protocol translation and multiplexing and supported basic network services, like switching Ethernet address monitoring in order to map them to network device ports and minimize traffic broadcasting) and user-based access control (strong user authentication and association with a network policy that allows use of specific applications). Nonetheless, the wide adoption of the SDN paradigm has motivated the enhancement of NOS with novel capabilities, like NOS scalability through state sharing between different instances, monitoring, policy conflict detection, and resolution between management applications and network virtualization. As the SDN paradigm is deployed in production networks, an interest is put toward mature control-plane platforms, supporting a richer set of network service. As a result, a series of vendor and service provider consortia have been formed currently in an effort to develop and support NOS platforms (like the OpenDaylight [29], ONOS [32], Ryu [33], and Floodlight [34] platforms). At the moment of writing, the standardization of the NI of the NOS still remains an open question. The abstraction varies between existing NOS, and it is highly influenced by the target deployment environment (e.g., a controller targeting carrier grade networks, like ONOS, requires a different set of control-plane functionalities, in comparison to a controller targeting virtualized data centers, like the VMware NSX [35]). Although a detailed discussion of the NI is beyond the scope of this paper, it is interesting to note that as the NI becomes more tightly coupled with the underlying controller function (e.g., routing versus security), its semantics will tend to converge to a common definition [3].

The development of the data-plane layer has created an interest in effective management-plane development environments using domain-specific languages (DSLs). Management-plane DSLs are built on top of the control plane and use the NI provided by the control plane. The novelty and effectiveness of the SDN approach has developed an interesting competition between programming language experts to define new DSLs with support for all the required programming primitives and semantics. This led to the development of multiple languages aiming to address different aspects of control-plane programming. For example, Netcore [36] provides a high-level forwarding policy language, Nettle [37] transforms the view of

control applications and focuses on changes in the state of network elements rather than event processing, while Maple [38] provides a scalable multicore scheduler and runtime policy optimizer for OpenFlow control to match available device resource configuration. Nonetheless, several programming languages have been developed by evolving existing languages, such as Flog [39], which combines ideas from FML [40] and Frenetic [41]. Research on SDN DSLs has explored also the applicability of different programming paradigm on the expressability of the management plane. With the exception of Pyretic [42], most high-level SDN programming languages adopt a declarative paradigm, then explore further specific programming models: functional programming [36], [38], [41], logic programming [39], [43], dataflow programming [40], and functional reactive programming [37], [44]. At the time of writing, no single language stands up to all the challenges imposed by SDN. We do not expect this situation to change in the future.

Research on management-plane applications has motivated solutions for a wide range of network problem. To exemplify how these solutions are leveraged through the SDN paradigm, we will focus on a common network problem; maintaining consistency during policy updates. The centralized nature of SDN introduces a significant problem in incremental policy update deployment. A policy update for a network path that spans across multiple switches can result in transient policy violations, if the processing of the flow table modification messages is not timely and ordered across all switches. Nonetheless, the semantics of the reconfiguration abstraction in existing commercial off the shelf (COTS) platforms is not designed to provide such update consistency semantics [45]. Traditional network control protocols support weak consistency models, using distributed eventual-consistent algorithms (e.g., routing protocols) [46]. In the context of SDN, multiple solutions have been proposed to address this problem, by introducing in the NOS NI transactional update interfaces. The NOS implementation of these interfaces aggregate policy updates, analyzes them for potential conflict during deployment, and schedules their deployment accordingly using two-phase commit algorithms [47]-[49].

#### **B. SI Programming Languages**

Existing SDN approaches have widely adopted the OpenFlow protocol [5] as the SI. Released as an open-source implementation that fulfilled a need, OpenFlow has become widely available in commercial SDN devices. OpenFlow holds an important position in its role as an early SDN enabler. It assimilates a low-level, assembly-like machine language, closely aligned with and limited by the underlying hardware. The burden remains on the programmer, who needs intimate understanding of the hardware (such as switch details and available resources), as well as behavioral details of the handling of overlapping rules and rule ordering. This was one of the incentives for

the development of the management layer languages. Nonetheless, such limitations reduce OpenFlow code reusability. Consequently, creating modular/reusable code is challenging and the development process is prone to error.

At the time of writing, OpenFlow does not have sufficient expressability to cover the entire functionality provided by network devices, nor can it optimize their performance. This is true even for devices having an architecture compliant with the OpenFlow specification. For this reason, another abstraction layer is often provided between the two. For example, Broadcom's OpenFlow dataplane abstraction (OF-DPA) [50] defines and implements a hardware abstraction layer that maps the Broadcom's StrataXGS switch architecture to the OpenFlow 1.3.1 switch and pipeline. Similar approaches are currently explored by other vendors. The protocol oblivious forwarding (POF) [51] proposal sets an ambitious goal to provide an abstraction table above the device driver, but also to extend OpenFlow's protocol-dependent instruction to be protocol independent. A prototype POF implementation is available for the Huawei's NE5000 core router, which uses the proprietary microcode for its network processor. Furthermore, P4 (an acronym for programming protocol independent packet processors) [52], [53] sets three more ambitious goals: switch reconfigurability in the field, protocol independence, and independence from underlying hardware. In this way, P4 operates as a complement to SDN protocols, like OpenFlow, and considers reconfiguration of the data plane to support (in target hardware or evaluation designs) specific operations that are then manipulated by such protocols as OpenFlow.

#### C. Data-Plane Programming Languages

While OpenFlow handles the low-level aspects of the data plane, it is not the language used to program widely used data-plane devices. Network processors, whose host processing units require special programs, were for many years using proprietary programming languages (e.g., Marvell's XLP [54], EZchip [55]). The use of specialized processing units, optimized for bandwidth, led to the development of different instruction set architectures by each company, exploiting the advantages of each architecture. In 2008, Cisco was the first company to introduce a network processor that was fully ANSI-C compatible [56]. This approach was later followed by Ericsson [57], and most recently by EZchip [58].

Several attempts have been made to go beyond assembler and C-like programming languages for packet processing. PacLang [59] was an early attempt for a highlevel data-plane language prototyped on the Intel IXP2400 network processor. Based around the premise of strong typing (explicit variable type casting, checked at compile time) and linearizable types (any object variable is used exactly once within the program, thus simplifying memory management), PacLang presented a transformation-based methodology to separate architecture details from the

high-level program specification. The application code was written in a high-level language and then matched to the network processor architecture using an architecture map, ping script. Compared to previous solutions for a single task or pipeline, a novelty of PacLang was its ability to handle multicore network processors.

PX [60] (and its earlier incarnation [61]) is a high-level language for specifying packet-processing requirements, designed for field-programmable gate array (FPGA) implementations. It is also focused on what should be done, rather than how, leaving the hardware implementation details to be handled by the compiler. The compiler, in turn, generates code in VHDL and Verilog hardware design languages (HDL).

While no implementation is available to date for network applications, functional languages also present a future direction for reconfigurable network devices. Languages such as Chisel [62] and HardCaml [63], which generate low-level Verilog or VHDL code, are suited for such purposes.

#### D. Proprietary Environments

While the predominant SDN realizations remain currently under the umbrella of the Open Networking Foundation (ONF) [64] or IETF [65], some organizations choose to have their own environments supporting the same concepts. This allows these organizations to maintain a proprietary environment, implementing mechanisms that best suit their hardware and software, easing customer migration and removing restrictions imposed by public standards or specifications.

Cisco's open network environment (ONE) tries to go beyond SDN and set the foundations for, what Cisco describes as, an Internet of Everything (IoE) [66]. Their approach does not reject SDN, but rather tries to extend it to create a better integrated solution for Cisco devices. Accordingly, Cisco's network processors (e.g., nPower X1 [67], Typhoon [68], and QFP [69]) are OpenFlow capable. The difference lies in the development environment underlying it, dubbed onePK [70]. onePK allows a programmer to write code in one of several languages (C, Java, Python) using a set of APIs that abstract the OS and network device internals. Effectively, onePK enables easy interoperability with multiple layers of the SDN model, as well as other interfaces and languages, like OpenFlow and HTTP-based services [71], either seamlessly or through plugins [72]. The onePK environment also integrates with Cisco's application-centric infrastructure (ACI), which operates at a higher architectural level.

A very different approach is taken by Xilinx's softwaredefined specification environment for networking (dubbed SDNet) [73]. SDNet assumes that the underlying hardware is completely programmable (e.g., FPGA), and uses this to implement programmability of the data plane. The concept contains a complete design flow, from SDNet high-level description language, through the SDNet hardware design

language compiler, to Xilinx's design tool (Vivado) that generates the FPGA implementation's bitstream. The dataplane packet processing units allow firmware updates between packets. While SDNet is not tied to a specific southbound programming language, it does not reject them either: the user may choose to implement, for example, OpenFlow protocol support in hardware, and provide custom code to support it.

Additional environments, such as Juniper's Junos Fusion, Huawei's SoftCom, and Arista's software-driven cloud networking (SDCN), exist, with various levels of maturity and conformance with ONF. The adoption of these (primarily commodity/closed-source) environments by the networking community is yet to be seen.

#### IV. RECONFIGURATION IN **ELECTRONIC SWITCHING**

In current electronic switching, software-defined networks commonly rely on header processing. Header processing is the stage where the header (the part of the packet that contains address and network-handling details) is identified and examined. This is also the stage where packet actions are decided, such as setting a packet's destination within the device (e.g., queue, flow, port), or selecting the number of replications of a packet. However, there are further reconfiguration aspects to switching, which are discussed in this section.

#### A. Header Processing

A networking element does not always require header processing. For example, a host computer attached to the network with a single-port network interface card (NIC) may forward all packets from the network to the central processing unit (CPU), and all packets from the CPU to the network, without further processing. However, this is rarely the case. Recall simple operations of our basic switch in Section II: as a packet enters a device, its header is parsed, matching rules are checked, and actions are applied to it. The analysis may examine specific bits or detect an expected format (Fig. 4), or perform a more sophisticated parsing. Clearly, the level of reconfiguration required for this stage may vary between devices. Devices that support only one header type may have little need for reconfiguration, but devices supporting more sophisticated header processing might benefit from the ability to dynamically reconfigure hardware to perform functions more effectively.

Highly reconfigurable systems could permit defining which protocols are admissible (or excluded), the number of headers within a packet to be looked up, or even describe complex lookup operations when multiple networking protocols are being used. Furthermore, reconfiguration flexibility allows adding support for new protocols. As new protocols emerge, a network operator may need devices to recognize these protocols and handle the packets accordingly.

It is instructive to consider a few examples of how network actions can be driven by the structure of packet headers. For example, a most basic admission action is "Should the packet be admitted or dropped?". Other example actions are to assign a packet to a specific destination output port, or to specify a quality-of-service queue within the device. Packets terminating within a device (e.g., exception packets) may have actions that differ from those for packets sent to a remote destination. The stage at which actions are assigned can also vary, yet three stages are commonly localized: The classification stage (where necessary information is extracted from the header, such as the protocol, the packet's source, and destination), the forwarding stage (where the destination queue and/or output port of the packet inside the device is decided), and the modification stage (where the header of the packet is being altered). The shared property of all these stages is that they require configuration, both of actions and of results.

The header processing module may conduct many further operations, from collecting statistics to security operations (e.g., dropping packets with a false source address). Such functions can be rich, varied, and almost arbitrarily sophisticated, attesting to a need for expressive forms of SDN.

Currently, the hardware involved in network systems support a variety of reconfiguration mechanisms. The simplest involves using registers for configuration, yet their use tends to be limited to enabling or disabling a function. A standard header processing configuration is implemented using tables or databases. The most common table is a forwarding table. The routing table is an example of dynamically configurable data structure associated with the routine operation of a router. During operation the router learns new IP addresses, along with a port assignment through which they are accessible. This information is added to the routing table and new packets arriving to the router are sent to the right port accordingly. As network connectivity changes over time, so does the routing table: entries are not only added, but also deleted or altered. While the routing table can be considered a stored state, the result of modifying the routing table is an operational reconfiguration: packet flows previously sent to port X may be sent to port Y as a result of an entry being modified, their content (e.g., header fields) may be modified, or e.g., they may be dropped.

Header parsing uses tables that are indexed by packet headers, e.g., destination IP addresses. Each entry in such tables contains specific primitive actions such as setting the packet's destination, drop the packet, etc. These tables used for header parsing require memory, which in turn scales in direct proportion to the number of entries in a table. For this reason, for many years these tables were implemented using external memory modules, using different memory technologies. Over time, shrinking silicon processes allow more and more on-chip memory. As

external memories not only add to a networking element's cost, but also to its power consumption and overall size, there is a considerable motivation for using on-chip memory to implement these tables. This trend in monolithic implementation stands in contrast with the progressive need to increase table size to accommodate more table entries. Consequently, some network and packet processing devices use external memories, while other contain all tables on-chip. A variant of those are configurable networking devices that allow selection between relatively small internal and larger external memories.

Network and packet processing devices which employ many tables and allow a large flexibility often face the challenge of meeting conflicting size requirements by different customers: one application will require table A to be large and table B to be small, whereas a second application will require a lot of entries in table B and no use of table A at all. This contradiction can be solved by sharing databases across a device: allowing a user to select the memory size for each table out of a shared pool. This approach is resonant to ones often used in FPGA devices, where the FPGA provides users with a shared pool of memory resources that can be utilized according to an implementation's needs.

The flexibility expected in header processing has grown over time. If two decades ago a static configuration was acceptable, and a decade ago marked the emergence of network processors, then today many devices claim to be fully programmable and highly flexible. This is largely driven by market forces, as chip vendors try to reach as many market segments as possible. In addition, users require programmability in order to be able to reconfigure their network over time, adding new protocols, altering configurations, and so on. While in the past network processors used proprietary processor architectures that maximize performance (e.g., Marvell's DataFlow architecture [74]), then today more and more network processors embed "traditional" RISC architectures (such as EZchip, Broadcom, Ericsson, Cisco). This trend is possibly another step toward the less intelligent programmable hardware driven by the SDN paradigm.

#### B. Traffic Management

Header processing is focused on where packets are sent. In contrast, traffic management is focused on how a stream of packets to a certain destination is being handled, which is commonly referred to as the quality of service (though traffic management is broader than that). Quality of service covers many parameters (such as bandwidth, latency, and jitter) and is provisioned using different types of mechanisms within a traffic management device (e.g., scheduling and rate limiting). As traffic management devices need to match the services bought by the user to the available resources, they tend to be highly configurable. Such devices require the ability to intimately configure and tweak resources, allowing every traffic flow to be assigned to a correct group of detailed servicing rules.

We distinguish between two classes of reconfiguration mechanisms: mechanisms that affect the way the device works, and mechanisms that set the way a specific traffic flow is handled within the device. The second type of configuration mechanism is typically easier to handle, since it is usually implemented within a table, written as part of the power up sequence. The entries in such a table indicate what different properties should be assigned per flow. Examples include setting the level of priority or the committed bandwidth.

Configuration mechanisms of the first type (that affect intrinsically how a device works) can vary significantly. For example, a scheduler may allow one or more scheduling schemes to be defined (such as strict priory versus weighted fair queuing [75], [76]), and weights need to be assigned to any flow or group of flows in a weighted scheduling scheme. Similarly, a traffic shaper needs to be assigned average and peak rates as well as a burst size [77].

Congestion management is another class of complex network operation amenable to (if not requiring) reconfiguration support. Example functions range from the simple setting of thresholds in different queue management schemes (such as random early detection [78], where a packet is dropped before being admitted to a filling queue) to rate adaptation (by methods such as explicit congestion notification [79] and quantized congestion notification [80]). Changing the traffic rate of a flow requires changing the configuration of thresholds and shaping parameters in a networking device, which in turn modifies the rate of a given flow (e.g., a congested flow).

Despite being a general paradigm, when OpenFlow was introduced and SDN got traction, the focus of data-plane research was on header processing. There is a growing understanding that other aspects of the data plane need to be defined as well. Furthermore, as the central management of SDN allows an end-to-end view of resource utilization across the network, using it to improve aspects of traffic management is called for. The use of the control plane for traffic management was well studied by different groups (as surveyed in [3] and [81]). Implementations of traffic management in the data plane, in hardware (as opposed to software-based solutions, such as QueuePusher [82]), are still rare. One example of such implementation was presented by Sivaraman et al. [83], who implemented SDN-enabled queue management in an FPGA. Further study of enabling traffic management in the data plane is still underway [84]. The lack of research done to date in this area is somewhat surprising, given that it was proposed as a characteristic of SDN a long time ago [1].

#### C. Switching Devices and Functions

The last building block of a switching device that we discuss is the switching unit. The most basic switching unit is the crossbar, which allows a dynamic connection between input/output (I/O) pairs between the ports of this network element. For this switching method to be

nonblocking (meaning all possible combinations of I/O pair assignments can be accommodated), it must be configurable, allowing inputs to change their paired outputs over time, e.g., allowing packets incoming on port N to be sent to any port *M*, according to their header. This type of switching is near instantaneous in electrical switching but can take milliseconds in some electromechanical photonic switches (discussed in Section VI-B). As crossbars (whose internal resource consumption grows quadratically with port size) fail to scale with the performance required in modern networks, other, more scalable, multistage switching architectures are gaining traction within current day systems (e.g., Clos [85] and Fat-Tree [86]).

Switching elements have several modes of use. For example, a network switching chip can work as a standalone device (with all its interfaces serving as ports), or it may be connected in a mesh with other identical devices (to create a system capable of higher radix, bandwidth or both). In less common cases, a device may connect to a larger fabric mesh to create a multiboard or a multichassis switch (e.g., using commercial devices such as Broadcom's BCM88750 and BCM88650 [87]). This is commonly achieved using modular (i.e., board or box) assemblies. In this case, the end user buys a module, which can be used in a variety of different ways. A fabric module can be configured to operate as a single-stage switch fabric in a standalone chassis, or as a first and last stage (but, for example, not middle stage) fabric switch, connecting to a different fabric chassis when placed in a multichassis system [88]. This type of a configuration allows scaling switching systems based around common building blocks, such as Huawei's NE5000E and Cisco's CRS-X, from a few terabits per second to hundreds of terabits per second [88]-[90].

Networking devices regularly offer more programmability and reconfiguration than available to the end users. Decisions taken during the design of a system, and settings applied during the assembly of devices within these systems, limit the level of reconfiguration available to the end user. Consider the example above, where devices used to create a multiboard or a multichassis may have programmable modes of operation. These devices also typically support multiple types of physical interfaces (e.g., 10 GbE, 40 GbE, 100 GbE), but once assembled on a given board the interface type is set to match the optical transceiver of this module and cannot be altered. This means the end user can alter the device or module's role within a system, but cannot alter the type of physical connectivity. This start-of-life setting benefits both silicon vendors and their customers: silicon vendors design and fabricate only one chip to support different market segments, whereas their customers use the device's programmability to manufacture and sell the most power-efficient, cost-effective networking system.

At the time of this writing, SDN-enabled electronic switching devices are increasingly being introduced by commercial vendors. This trend is also emerging in the latest photonic switches discussed in Section VI.

#### V. TECHNOLOGIES FOR RECONFIGURABLE NETWORK SYSTEMS

Several types of technologies are applicable for networking devices. In considering how reconfigurable systems approach could be used more effectively, we consider a spectrum that trades configurability for performance, and what we might do to better achieve both. This section provides an overview of these considerations and discusses the trends over the last few decades.

Let us first describe the spectrum of programmability and configurability. The most programmable type of device is a general purpose CPU. Completely programmable, it allows any programmer to create a networking device of his own design, where only the device interfaces set the limitations of the CPU-based system.

Network processors (we omit graphics processing units from this discussion) are less programmable than CPUs, as they are designed for a specific purpose, and their architecture matches that purpose. Network processors vary considerably in their architecture, therefore it is hard to make generalizations about their level of programmability: some network processors force a single datapath structure and allow programming the actions taken in every stage of the datapath, whereas others allow flexibility in the structure the datapath itself. The level of expertise required to program a network processor is higher than required to program a CPU, as the programmer often needs to write (device-specific) programs in order to configure each processing unit within the network processor.

We consider traditional FPGAs to be less programmable than network processors. An FPGA device is built from a set of resources (programmable logic blocks, memory blocks, and I/O). Using HDL (or high-level languages generating HDL descriptions) a user can design the FPGA to perform any operation, limited only by the available resources. Once completed, the design is then downloaded to the FPGA device. Once a resource is configured to work in a certain way, it will maintain this function until the device is powered off or the device is reprogrammed. This limitation on the use of a resource within the FPGA makes the FPGA less programmable than a network processor.

FPGA vendors offer processing cores embedded within the FPGA (e.g., [91] and [92]). These processing cores can be either soft cores (built using the FPGA's general purpose logic), or hard cores (built from dedicated silicon) [93]. Hard core processors (e.g., [94]) typically offer a better performance than softcore processors (e.g., [95] and [96]), however their dedicated silicon presents a waste of resources for FPGA designs that do not require a processor. Implementing a networking device over an FPGA requires a larger set of skills than programming a network processor. Even when using high-level programming languages, the user needs a deeper understanding of hardware aspects. The implementation of an FPGA (including simulation, synthesis, and routing) requires a set of skills not traditionally possessed by software engineers.

The least configurable devices are application-specific integrated circuits (ASICs) and COTS networking devices. While the level of reconfiguration of these devices varies, from highly configurable to completely transparent, as a group they are far less configurable than other solutions. COTS devices provide a closed feature set that the user may choose if and how to use, but the function itself is rarely programmable. Some contemporary high-end devices introduce a level of programmability into their packet processing units, using processing cores, however we classify those as a hybrid with microprocessors. While using a COTS device often requires the least expertise, designing one is the most challenging. It engages people with a wide set of expertise, from frontend and backend designers to embedded software engineers. Note the distinction that we make here between CPU and COTS networking devices: CPUs share with COTS devices a very long and expensive design cycle, but once CPUs reach the market, the customer can use them for a wide range of applications. A COTS networking device has its application set during the design stage, and it cannot be changed after that. This also reflects on the level of risk: if a bug is found in a networking device implemented over a CPU, the effort required to fix the bug is minimal. Fixing a bug in a COTS device can have an indeterminate complexity, often requiring changes in the manufacturing masks or even a new device fabrication, costing millions of dollars.

#### A. Evolution of Networking Devices Bandwidth

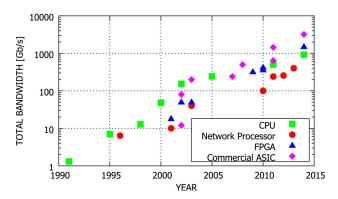

While CPUs offer the best level of programmability, they are not present in all networking devices. High levels of programmability are mostly seen in slower devices, while the highest bandwidth is commonly provided by the least configurable devices. Economic drives propose one reason for this phenomenon, but a technological insight is provided in Fig. 5. This figure presents the evolution of aggregated bandwidth of networking devices over several decades, starting from 1 Gb/s of the early 1990s to contemporary performance levels exceeding 1 Tb/s. As the figure shows, from the 1990s, CPUs (the most programmable devices) provided the best performance. Over time COTS devices (the least reconfigurable) managed to deliver the highest bandwidth. To better understand this conclusion, we explain the details of the figure.

For network processors and COTS networking devices, we use the manufacturer's declaration of bandwidth. For FPGAs, we present the maximal theoretical bandwidth, calculated using the IEEE 802.3 standards methodology where the quantity of I/O that can be used by a networking interface is multiplied by its maximal frequency. The definition of bandwidth per CPU is the product of device's bus width and core frequency, for a single core. Each point in the graph presents the "best of breed" performance for a given device type at a particular snapshot in time. All known devices available on the market to date were considered, including but not limited to Intel, AMD,

Fig. 5. Evolution of networking device bandwidth. In the last decade, the least programmable devices (COTS) provided the highest bandwidth performance, whereas the most programmable devices (CPU) made the least improvement.

EZchip, Netronome, Broadcom, Marvell, Mellanox, Altera, and Xilinx.

For CPUs, we calculate the effective bandwidth as the product of bus width and core frequency, as it is an indication of the internal pipe bandwidth as well as the possible packet rate (the number of packets processed every second). Although multicore processing was the direction taken to improve CPU performance, the product of the above bandwidth and the number of cores is not equal to the total device bandwidth. The internal communication bus of multicore CPUs is not designed to match the core bandwidth, even given optimizations [97]. As the multicore communication is the primary bottleneck, and its throughput is less than a single core's, we present a single core bandwidth and consider intercore communication a challenge for future networking initiatives, such as the Intel Omni-Path fabric [98].

Fig. 5 also reveals that in the previous century, CPU performance led all other solutions, while the last decade shows a more modest improvement of datapath bandwidth performance per core. In a comparison of 2007 and mid-2015 best-in-breed CPUs across all four SPEC CPU2006 benchmarks [99] we make an important performance observation. For whole-system performance, the speed benchmarks (CINT2006 and CFP2006) improved by a factor of approximately four and the throughput benchmarks (CINT2006rate and CFP2006rate) by a factor of 15, yet the relative performance per core improved by less than two, and the relative throughput performance per core improved by less than a factor of four. This difference also contributed to the emergence of network processors.

ASIC/COTS devices have played an interesting role in the evolution of network devices. A single modern network device may consist of many types of high end silicon devices, e.g., traffic managers (implementing packet rate limiters such as described earlier) or packet processors (devices implementing header parsing and header-field lookup to trigger specific processing). Yet the highest bandwidth capacity is always presented by the switching devices (those devices that, having the highest port count, provide port-to-port connectivity). The lower the complexity of the device, the fewer are the features beyond just switching, and the higher its bandwidth. The complexity of the device impacts both silicon area and difficulty in achieving a design that meets all the criteria. This drives devices toward simplicity, reducing features, in order to improve performance. This optimization of the ASIC and COTS devices is evident in comparison with network processors, which are built in the same semiconductor processes and subject to the same manufacturing constraints as CPUs, FPGAs, and other devices. It should be noted that the growth of bandwidth in COTS devices is tightly related to the mechanical aspects of the target switching systems. The bandwidth is often a multiplication of 24 ports times the maximal interface speed available, as this is the number of ports fitting a front panel of a card in a 19-in rack. Thus, 24, 48, and 96 ports are commonly used for port count, with the addition of a few uplink and management ports.

FPGAs have shown a consistent improvement over the last decade, with a steep increases in performance. On the other hand, the graph also demonstrates why FPGAs do not gain more traction with system vendors: the place where the FPGAs match the COTS devices performance is always at the same time or after COTS devices became available on the market. This means that the FPGA-based design will only start when a COTS-based design is already available. We account for early access to FPGA technology by large vendors and the reduced design cycle time of FPGA. However, eventually the networking devices need to be tested and validated in the lab, which can take a considerable amount of time. In order to replace COTS devices, FPGA devices need to be available a couple of years ahead of COTS devices with the same clock frequency (and other performance characteristics). Altera's Stratix 10 is an example of such an attempt, as Altera gained early access to manufacture it in 14 nm by an Intel semiconductor fabrication plant [100].

The design of a networking device is more than just interface bandwidth and clock frequency. Other FPGA resources (e.g., logic elements, embedded block memories, etc.) need to match those of COTS networking devices. The FPGA must provide a superset of all these resources or the design will not be able to carry the required feature set. This raises the complexity and cost requirements of FPGAs. Having said this, we prefer not to engage in a direct comparison of FPGA to COTS devices as we think a fair comparison is difficult. This is primarily due to the fact that simple metrics (such as gate count) do not adequately capture the true capabilities of an FPGA.

#### B. High-Speed Interface Adoption By **Networking Devices**

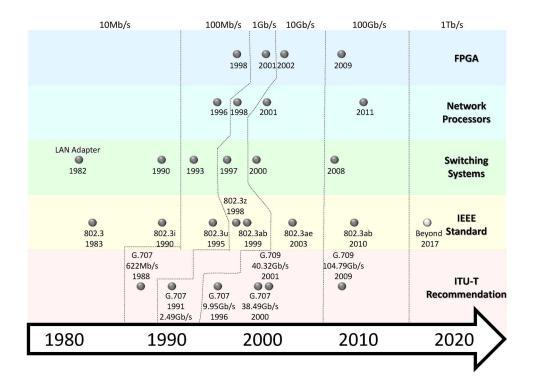

Fig. 6 presents the adoption of networking interface by different classes of networking devices over time. In this

Fig. 6. High-speed interfaces adoption by networking devices. Commercial switching systems tend to adopt new high-speed interfaces before a standard is concluded. FPGA devices do not claim support of new interfaces before a standard is completed.

figure, we focus on members of the IEEE 802.3, ITU-T G.707/Y.1322, and ITU-T G.709/Y.1331 standards families, starting with the basic 10-Mb/s IEEE 802.3 standard, and spanning the higher speeds projected by (at the time of writing) future standards. Interfaces composed from several parallel lanes, such as 4 × 3.125 Gb/s XAUI, are considered by their aggregated bandwidth (e.g., 10 Gb/s). The figure shows over time (x-axis) when a particular technology class achieved a particular performance plateau. The introduction of the new IEEE and ITU-T standards is shown by the two bottom rows. A particular point on the graph indicates an approximate point in time of "initial adoption," when products that embodied that interface performance level were available from the designated class ("FPGA," "network processors," "switching systems"). We choose to refer here to "switching systems" rather than ASIC/COTS devices, as most COTS switching devices do not connect directly to the network, but instead are interconnected with a vendor-specific (non-IEEE 802.3x or ITU-T G.709/Y.1331) interface, such as Interlaken [101] or SPI4.2 [102]. As such, the vendor-specific solutions more readily achieve targeted performance levels between their own components using proprietary ASICs.

While one would have expected the networking systems to be the last to come into the market, as their design cycle is unlikely to exceed the availability of silicon devices, the contrary thing happens: since the mid-1990s, commercial systems always came into the market ahead of

the official announcement of standards. While this is driven by companies wishing to gain customers by being first-to-market, this also relates to the long life-cycle defining standards and the involvement of vendors in this process. This involvement allows them to complete their design ahead of the publication and wide availability of the standard. The introduction of new standards varies significantly between standardization bodies. As Fig. 6 shows, ITU-T recommendations were once ahead of IEEE by up to seven years. While we cannot attest to the reason, we believe it is the combination of the focus of ITU-T on optical communication rather than electrical, and the narrow market segment aimed by the G.707 and G.709 standards (i.e., optical transport networks), which allowed fewer requirements and faster consolidation.

Network processors appear also to follow the same trend: being early in the market, available to the system designers that require them. An anomaly is observed for the introduction of network processors supporting 100-Gb/s interfaces, announced later than the standards. This is possible as several network processing devices announced in 2010 (the year of the IEEE 802.3ba standard) were not able to reach an aggregated 100-Gb/s bandwidth, and the one that did (EZchip NP-4) used an Interlaken interface (an interconnect protocol driven by Cisco and Cortina Systems).