# Scalable Fabrication, Characterisation and Critical Interface Simulation of $ULTRARAM^{TM}$ Memory Devices

### Xiuxin Xia

Supervisor:

Prof. Manus Hayne

Department of Physics

A thesis submitted for the degree of Doctor of Philosophy

July, 2025

# Scalable Fabrication, Characterisation and Critical Interface Simulation of $ULTRARAM^{TM}$ Memory Devices

Xiuxin Xia July, 2025

#### Abstract

In this work, the design, fabrication and characterisation of scalable ULTRARAM $^{TM}$  aiming at 50 nm gate dimension are reported, in conjunction with simulations of the interface alloying of the triple-barrier resonant-tunnelling (TBRT), aiming at the scaling-down of the feature size of the memory devices for commercialisation.

ULTRARAM<sup>TM</sup> is a non-volatile, III-V based compound-semiconductor, charge-storage memory in which the oxide barrier that separates the floating gate from the channel in flash is replaced by the TBRT structure that exploits the 2 eV band offset between InAs and AlSb. This empowers ULTRARAM<sup>TM</sup> to operate at low voltage and high speed, with high endurance, low disturbance and ultra-low switching energy.

Multiple batches of memory devices were fabricated alongside the optimisation of the self-aligned design. Two key improvements shape the final processing flow. The introduction of all-dry etching enables the nanometre scalability of the memory design for the first time and the employment of laser interferometry in end-point detection allows enhanced accuracy of etching to the 10 nm-thick channel. The characterisation of the as-fabricated devices demonstrated stable performance with memory windows of  $\sim 10~\mu\text{A}$  at room temperature and a minimum pulse duration 5 ms was obtained, indicating the success of improvements made in the refining of the fabrication flow. A lingering issue with the gate-drain leakage through dielectric due to the problematic gate metal that arose during the legacy method is solved, and a synchrotron X-ray nano-probe analysis was conducted in an attempt to understand the failure mechanism of the devices.

A resistive-gap hypothesis is proposed to explain the poor performance observed

in as-fabricated devices. A compact device design is then proposed to address the issue and preliminary validation of the fabrication flow shows promising results where the resistive gap is substantially reduced from  $\sim 5~\mu \mathrm{m}$  to 385 nm, a factor of ten smaller than the previous design. This is expected to further improve the memory readout performance.

Simulation by nextnano software using the multi-scattering Büttiker (MSB) probe formulism was carried out to investigate robustness of TBRT operation against intermixing after concerns were raised as a result of transmission electron microscopy (TEM) images. All scenarios, including alloying at both barrier and quantum well layers, show only slight impact on the memory operation voltage but no undermining of the TBRT function, evidencing the resilience of the TBRT structure against the growth imperfections or fluctuations, in strong support for the ULTRARAM<sup>TM</sup> concept. The interplay of these findings indicates ULTRARAM<sup>TM</sup>'s potential as a viable emerging universal memory and its way to practical application in the not too distant future.

## Acknowledgements

I would like to express my sincere gratitude to Professor Manus Hayne for his invaluable support, guidance, and patience throughout the course of my PhD studies. His encouragement, particularly during the challenging phases of scaling design, as well as his insightful discussions, have been instrumental to this work.

My heartfelt thanks also go to Dr Peter Hodgson for his continuous efforts in improving wafer growth and optimisation, a fundamental aspect of this study. I am especially grateful to Dr Dominic Lane, Dr Serdar Tekin, Dr Samuel Jones, Dr Jonathan Hall, and Gizem Acar for the many hours spent in the cleanroom and for their invaluable discussions and technical assistance. I extend my sincere appreciation to Garry Vernon for the timely support provided with cleanroom equipment.

I am grateful to Professor Benito Alén for granting me the opportunity to be part of the QUANTIMONY project. I would also like to thank Professor Richard Beanland and Dr Francisco Alvarado for their support with TEM analysis and for warmly welcoming me during my secondment at the University of Warwick. In addition, I appreciate the valuable assistance of Dr Stefan Birner and Takuma Sato with nextnano software support, which was essential to the development of the simulation work.

Special thanks to Dr Samuel Jarvis for the collaboration on XPS measurements, and to Dr Richard Wilbraham for FIB-SEM imaging support. I am also grateful to all collaborators at ESRF for facilitating the beamline measurements. My thanks extend to the staff and fellow students in the Department of Physics, as well as across the project, for their collaboration and support throughout the research.

Finally, I am deeply thankful to my family for their unwavering support, understanding, and patience over the past four years. To them, I am profoundly grateful.

## Declaration

I declare that, except where specific reference is made to the work of others, the work presented in this thesis is, to the best of my knowledge and belief, original and my own work. The material has not been submitted, either in whole or in part, for a degree at this, or any other university.

Xiuxin Xia, July 2025

## **Publications and Presentations**

#### Articles

Critical Interface Simulation of ULTRARAM<sup>™</sup> Memory Devices, in preparation.

#### Patent-pending

M. Hayne, P. Hodgson and X. Xia, Improved Memory Device, P00579, submitted. (2024)

#### Conferences

- Oral presentation at UK Semiconductors, July 2022, Sheffield, UK, Scaling of ULTRARAM™ III- Sb charge-storage devices for non-volatile random access memories.

- Oral presentation at WOCSDICE-EXMATEC, May 2023, Palermo, Italy, An optimised fabrication flow for scaling of ULTRARAM™ devices.

- Oral presentation at UK Semiconductors, July 2023, Sheffield, UK, Submicron scaling of ULTRARAM™ III- Sb charge-storage devices for non-volatile random-access memories.

- Oral presentation at UK Semiconductors, July 2024, Sheffield, UK, UL-TRARAM™: Advances in scaling and array fabrication.

- Oral presentation at IQUARUS, San Sebastián, Spain, July 2024, Scaling of ULTRARAM™: Fabrication, characterization and simulation of III-V compound-semiconductor non-volatile memory.

- Poster at NVMTS, October 2024, Busan, South Korea, Development of scaling for ULTRARAM™.

- Poster at IQUARUS, Simulations of the triple-barrier resonant-tunnelling heterostructure for ULTRARAM $^{\text{TM}}$  memory.

# Contents

| 1 | Intr | roduct | ion                                                             | 1  |

|---|------|--------|-----------------------------------------------------------------|----|

|   | 1.1  | Motiv  | ation                                                           | 1  |

|   | 1.2  | Synop  | sis                                                             | 2  |

| 2 | Me   | mory l | Devices                                                         | 4  |

|   | 2.1  | Field- | Effect Transistor                                               | 4  |

|   |      | 2.1.1  | Metal-Oxide-Semiconductor Field-Effect Transistor               | 4  |

|   |      | 2.1.2  | Floating Gate Metal-Oxide-Semiconductor Field-Effect Tran-      |    |

|   |      |        | sistor                                                          | 8  |

|   |      | 2.1.3  | Logic Gates and Memory Auxiliaries                              | 12 |

|   | 2.2  | Memo   | ory Classifications                                             | 14 |

|   |      | 2.2.1  | The Memory Hierarchy                                            | 14 |

|   |      | 2.2.2  | Static Random-Access Memory                                     | 16 |

|   |      | 2.2.3  | Dynamic Random-Access Memory                                    | 18 |

|   |      | 2.2.4  | Flash Memory                                                    | 21 |

|   |      | 2.2.5  | Advances in Memory Development                                  | 25 |

|   |      |        | 2.2.5.1 Architecture Evolution                                  | 26 |

|   |      |        | 2.2.5.2 Emerging Memories                                       | 31 |

|   | 2.3  | ULTR   | $ARAM^{TM}$                                                     | 36 |

|   |      | 2.3.1  | Multiple-Barrier Resonant-Tunnelling                            | 39 |

|   |      | 2.3.2  | Primary Triple-Barrier Resonant-Tunnelling Design               | 43 |

|   |      | 2.3.3  | $\operatorname{ULTRARAM}^{\scriptscriptstyle{TM}}$ Fundamentals | 50 |

| 3 | Res | earch   | Methods                                               | 54  |

|---|-----|---------|-------------------------------------------------------|-----|

|   | 3.1 | Epita   | xial Growth                                           | 54  |

|   | 3.2 | Fabric  | cation                                                | 56  |

|   |     | 3.2.1   | Optical Mask Lithography                              | 56  |

|   |     | 3.2.2   | Laser Writer                                          | 58  |

|   |     | 3.2.3   | Reactive-Ion Etching                                  | 59  |

|   |     | 3.2.4   | Inductively Coupled Plasma Etching                    | 60  |

|   |     | 3.2.5   | Atomic Layer Deposition                               | 64  |

|   |     | 3.2.6   | Plasma-Enhanced Chemical-Vapour Deposition            | 66  |

|   |     | 3.2.7   | Thermal Evaporation                                   | 67  |

|   |     | 3.2.8   | Sputtering                                            | 71  |

|   |     | 3.2.9   | Wire Bonding                                          | 72  |

|   | 3.3 | Chara   | acterisation                                          | 73  |

|   |     | 3.3.1   | Probe Station                                         | 73  |

|   |     | 3.3.2   | Surface Characterisation Technique                    | 75  |

|   |     | 3.3.3   | Transmission Electron Microscopy and Focused Ion Beam | 77  |

|   |     | 3.3.4   | X-Ray Nano-Probe Technique                            | 77  |

|   | 3.4 | Simul   | ation                                                 | 78  |

|   | 3.5 | Summ    | nary                                                  | 79  |

| 4 | Fab | ricatio | on and Scaling of ULTRARAM™                           | 80  |

|   | 4.1 | Scalin  | ng Scheme                                             | 80  |

|   | 4.2 | Fabric  | cation and Self-Aligned Design                        | 82  |

|   |     | 4.2.1   | Process Flow with Wet-Etching                         | 82  |

|   |     | 4.2.2   | Scalable Route with All-Dry-Etching                   | 90  |

|   |     | 4.2.3   | Improved Self-Aligned Structure                       | 96  |

|   | 4.3 | Chan    | nel Etching with End-Point Detection                  | 105 |

|   |     | 4.3.1   | Layout Design Improvement                             | 105 |

|   |     | 4.3.2   | Recipe Optimisation                                   | 106 |

|   |     | 4.3.3   | Laser Interferometry with Shorter Wavelengths         | 109 |

|   | 4.4 | Summary                                                                          | 112 |

|---|-----|----------------------------------------------------------------------------------|-----|

| 5 | Mea | asurements and Characterisation                                                  | 114 |

|   | 5.1 | Gate Leakage                                                                     | 114 |

|   | 5.2 | Channel Characterisation                                                         | 119 |

|   |     | 5.2.1 Transfer Length Method                                                     | 119 |

|   |     | 5.2.2 Field-Effect Transistor Measurement                                        | 123 |

|   | 5.3 | Memory Characterisation                                                          | 125 |

|   |     | 5.3.1 Measurement Configuration                                                  | 126 |

|   |     | 5.3.2 Device from Batch XPH 1823                                                 | 128 |

|   |     | 5.3.3 Device from Batch XPH 2213                                                 | 133 |

|   |     | 5.3.4 Device from Batch XPH 2318                                                 | 135 |

|   | 5.4 | X-Ray Nano-Probe Technique Analysis                                              | 137 |

|   |     | 5.4.1 X-Ray Absorption Near Edge Structure                                       | 137 |

|   |     | 5.4.2 X-Ray Fluorescence                                                         | 138 |

|   | 5.5 | Summary                                                                          | 139 |

| 6 | Sim | nulation by nextnano                                                             | 141 |

|   | 6.1 | Background                                                                       | 141 |

|   | 6.2 | Channel Design and Heterojunctions                                               | 144 |

|   | 6.3 | Simulations of the Tunnelling Layers in ULTRARAM $^{\!\!\top\!\!\!M}$ Devices $$ | 146 |

|   |     | 6.3.1 Interface Alloying                                                         | 147 |

|   |     | 6.3.2 Barrier Alloying                                                           | 148 |

|   |     | 6.3.3 Quantum Well Alloying                                                      | 151 |

|   | 6.4 | Summary                                                                          | 154 |

| 7 | Con | nclusions and Future Work                                                        | 156 |

|   | 7.1 | Conclusions                                                                      | 156 |

|   | 7 2 | Futuro Work                                                                      | 158 |

| Appen   | dix A Fabrication Details                | 160   |

|---------|------------------------------------------|-------|

| A.1     | Epitaxial Designs                        | . 160 |

| A.2     | Etching Recipes                          | . 164 |

| A.3     | Lithography Details                      | . 166 |

| A.4     | Dielectric Recipes                       | . 168 |

| Appen   | dix B Basics of Simulation               | 170   |

| B.1     | Etching Simulation                       | . 170 |

| B.2     | nextnano Simulation                      | . 172 |

|         | B.2.1 Material Parameters                | . 172 |

|         | B.2.2 Interpolation of Ternary Compounds | . 172 |

| Refere: | nces                                     | 174   |

## Glossary of Abbreviations and Acronyms

AI Artificial intelligence

ALD Atomic layer deposition

ALU Arithmetic-logic unit

**BEOL** Back end of line

**CFET** Complementary field-effect transistor

CMOS Complementary metal-oxide-semiconductor

CPU Central processing unit

CTLM Circular transfer length method

**DELTA** Depleted lean-channel transistor

**DI** Deionised

**DIMM** Dual in-line memory module

**DRAM** Dynamic random-access memory

**DUT** Device under test

**EBL** E-beam lithography

ECCI Electron channelling contrast imaging

**EDS** Energy dispersive spectroscopy

**EEPROM** Electrically erasable programmable read-only memory

**EFO** Electronic flame off

**EPROM** Erasable programmable read-only memory

**EOS** Eletron optical system

**FEOL** Front end of line

**FET** Field-effect transistor

Ferandom-access memory

FGMOSFET Floating gate metal-oxide-semiconductor field-effect transistor

FIB Focused beam ion

**FN** Fowler-Nordheim

GAAFET Gate-all-around field-effect transistor

**HBM** High bandwidth memory

**HCI** Hot carrier injection

IC Integrated circuit

ICP Inductively coupled plasma

IMC In-memory computing

IPA Isopropyl alcohol

LOR Lift-off resist

LW Laser writer

MAC Multiply and accumulate

MBE Molecular-beam epitaxy

ML Machine learning

MLC Multi-level cell

MOSFET Metal-oxide-semiconductor field-effect transistor

MRAM Magnetic random-access memory

MSB Multi-scattering Büttiker

MTJ Magnetic tunnel junction

**NEGF** Non-equilibrium Green's function

NDR Negative differential resistance

NMOS N-type metal-oxide-semiconductor field-effect transistor

**NVM** Non-volatile memory

**OES** Optical emission spectroscopy

PC Personal computer

PECVD Plasma-enhanced chemical-vapour deposition

PLC Penta-level cell

PMMA Polymethyl methacrylate

PMOS P-type metal-oxide-semiconductor field-effect transistor

PRAM Phase change random-access memory

**PROM** Programmable read-only memory

QLC Quad-level cell

RAM Random-access memory

**ReRAM** Resistive random-access memory

RF Radio frequency

**RHEED** Reflection high-energy electron diffraction

RIE Reactive-ion etching

ROM Read-only memory

SEM Scanning electron microscopy

SGT Surrounding-gate transistor

SLC Single-level cell

SMU Source measure unit

**SOI** Silicon on insulator

**SOT** Spin-orbit torque

SRAM Static random-access memory

SSD Solid-state drive

STT Spin transfer torque

TBRT Triple-barrier resonant-tunnelling

TEM Transmission electron microscopy

TLC Triple-level cell

TLM Transfer length method

TMA Trimethylaluminium

TSV Through-silicon via

UV Ultraviolet

**XANES** X-ray absorption near edge structure

XPS X-ray photoelectron spectroscopy

XRF X-ray fluorescence

**1T1C** One transistor and one capacitor

**1T1MTJ** One transistor and one magnetic tunnel junction

**1T1R** One transistor and one resistor

# List of Tables

| 2.1 | Performance specifications of various memories [28–31]                          | 15  |

|-----|---------------------------------------------------------------------------------|-----|

| 2.2 | Cell types and binary values                                                    | 22  |

| 2.3 | Comparison between NOR and NAND flash                                           | 24  |

| 2.4 | Representative metrics of emerging memories [7, 143, 197–201]. *                |     |

|     | from the extrapolated data; ** from simulation based on 20-nm node.             | 37  |

| 4.1 | Detailed layout of XPH 1452 wafer for ULTRARAM $^{TM}$ , utilised in            |     |

|     | the wet-etching fabrication.                                                    | 83  |

| 4.2 | Detailed layout of XPH 1823 wafer for ULTRARAM $^{\text{TM}}$ , featuring the   |     |

|     | introduction of isolation layers                                                | 91  |

| 4.3 | Detailed layout of XPH 2318 wafer for ULTRARAM $^{\intercal M}$ , incorporating |     |

|     | undoped InAs channel                                                            | 98  |

| 5.1 | Detailed layout of XPH 1896 wafer for ULTRARAM $^{\text{TM}}$ , illustrating    |     |

|     | the typical design of the floating gate, TBRT, channel, and isolation           |     |

|     | structures                                                                      | 115 |

| 5.2 | Measured values extracted from the CTLM measurement of XPH                      |     |

|     | 2318 wafer                                                                      | 123 |

| 6.1 | Layer details of the TBRT configuration for nextnano simulation                 | 147 |

| A.1 | Detailed layout of XPH 1452 wafer for ULTRARAM $^{\intercal M},$ utilised in    |     |

|     | the wet-etching fabrication.                                                    | 160 |

| A.2  | Detailed layout of XPH 1823 wafer for ULTRARAM <sup><math>M</math></sup> , featuring the                                        |

|------|---------------------------------------------------------------------------------------------------------------------------------|

|      | introduction of isolation layers                                                                                                |

| A.3  | Detailed layout of XPH 1896 wafer for ULTRARAM $^{\!\top\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

|      | typical design of the floating gate, TBRT, channel, and isolation layers. $161$                                                 |

| A.4  | Detailed layout of XPH 2093 wafer for ULTRARAM $^{\!\top\! M}.$ The addi-                                                       |

|      | tional layers between the channel and the isolation unit are introduced                                                         |

|      | to improve signal identification during ICP etching                                                                             |

| A.5  | Detailed layout of XPH 2213 wafer for ULTRARAM $^{\!\top\!\!M},$ designed with                                                  |

|      | increased channel thickness                                                                                                     |

| A.6  | Detailed layout of XPH 2318 wafer for ULTRARAM $^{\text{TM}},$ incorporating                                                    |

|      | undoped InAs channel                                                                                                            |

| A.7  | ICP recipes for etching various materials used in the ULTRARAM $^{\top M}$                                                      |

|      | fabrication                                                                                                                     |

| A.8  | RIE recipes for various materials used in the ULTRARAM $^{\top \! \! \! \! M}$ fabrica-                                         |

|      | tion. The etching time for $Si_3N_4$ , $Al_2O_3$ , Ta and PMMA is based the                                                     |

|      | nominal thickness of 180 nm, 15 nm, 63 nm and 200 nm, respectively. $166$                                                       |

| A.9  | Solutions used for wet-etching of InAs and AlSb                                                                                 |

| A.10 | Spinning parameters for photoresists used in this work                                                                          |

| A.11 | Developing procedures for different photoresist combinations 167                                                                |

| A.12 | PECVD recipe of each step for $\mathrm{Si}_3\mathrm{N}_4$ deposition used in the UL-                                            |

|      | $TRARAM^{TM}$ fabrication                                                                                                       |

| A.13 | ALD deposition recipes for $\mathrm{Al_2O_3}$ used in the ULTRARAM <sup>TM</sup>                                                |

|      | fabrication                                                                                                                     |

| B.1  | Optical parameters of InAs, AlSb and GaSb used in the etching                                                                   |

| D.1  | simulation with various wavelengths [262]                                                                                       |

| Dη   |                                                                                                                                 |

| B.2  | Optical parameters of Al <sub>0.5</sub> Ga <sub>0.5</sub> Sb and Si used in the etching                                         |

| Dэ   | simulation with various wavelengths [262]                                                                                       |

| B.3  | nextnano material parameters for the simulation                                                                                 |

| B.4  | Bowing parameters for the simulation                                                                                            |

# List of Figures

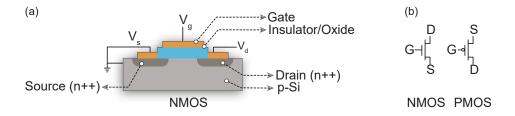

| 2.1 | (a) Schematic of an n-type MOSFET. $V_{\rm g},V_{\rm d}$ and $V_{\rm s}$ stand for the                  |    |

|-----|---------------------------------------------------------------------------------------------------------|----|

|     | gate bias, the drain bias and the source bias, respectively. (b) Circuit                                |    |

|     | symbols for NMOS and PMOS. G, the gate; D, the drain; S, the source.                                    | 5  |

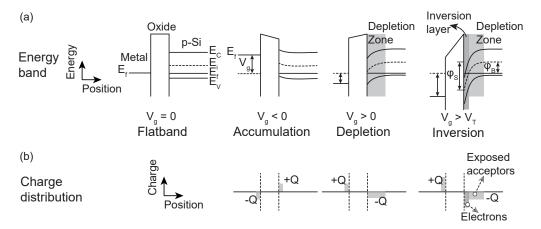

| 2.2 | Illustration of MOSFET (a) band diagram and (b) charge distribution                                     |    |

|     | for different bias conditions. There is opposite band bending near                                      |    |

|     | surface for positive and negative conditions. Flat band, accumulation,                                  |    |

|     | depletion and inversion conditions are depicted. $E_{\rm C}$ , the conduction                           |    |

|     | band energy; $E_{\rm i}$ , the intrinsic energy level; $E_{\rm f}$ , the Fermi level; $E_{\rm V}$ , the |    |

|     | valence band energy; $V_g$ , the gate voltage; $V_T$ , the threshold voltage;                           |    |

|     | Q, the charge; $\varphi_{\rm S}$ , the surface potential; $\varphi_{\rm B}$ , the bulk potential        | 6  |

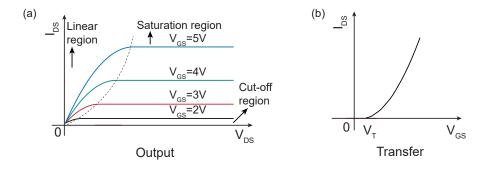

| 2.3 | (a) Output curves at various gate voltages of an n-channel enhance-                                     |    |

|     | ment MOSFET. The dashed line denotes the boundary between the                                           |    |

|     | linear region and the saturation region. (b) Transfer characteristics                                   |    |

|     | of an n-channel enhancement MOSFET. $I_{\rm DS},V_{\rm DS}$ and $V_{\rm GS}$ represent                  |    |

|     | the source-drain current, the source-drain voltage and the gate-source                                  |    |

|     | voltage, respectively                                                                                   | 8  |

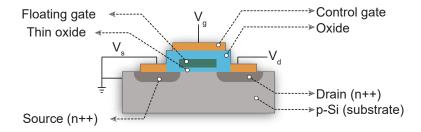

| 2.4 | Detailed architecture of a typical FGMOSFET. $V_s$ , the source bias;                                   |    |

|     | $V_d,$ the drain bias; $V_g,$ the gate bias                                                             | 9  |

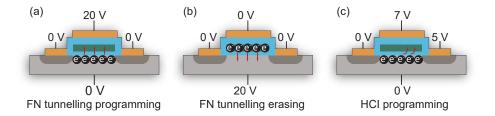

| 2.5 | Illustration of programming and erasing processes for FGMOSFETs.                                        |    |

|     | (a) FN tunnelling programming. (b) FN tunnelling erasing. (c) HCI                                       |    |

|     | programming                                                                                             | 10 |

|     |                                                                                                         |    |

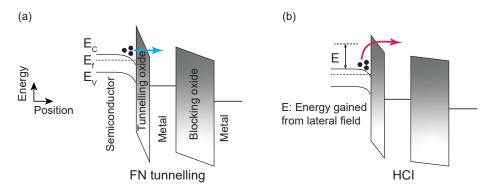

| 2.6  | Band diagram of (a) FN tunnelling and (b) HCI in an FGMOSFET                               |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | structure. The FN tunnelling is a field emission while HCI involves                        |    |

|      | both field emission and thermionic emission. $E_{\rm C},~E_{\rm f}$ and $E_{\rm V}$        |    |

|      | correspond to the conduction band, the Fermi level and the valence                         |    |

|      | band, respectively.                                                                        | 11 |

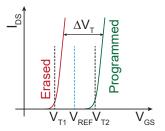

| 2.7  | $I_{DS}\text{-}V_{GS}$ characteristics of an FGMOSFET for programmed and                   |    |

|      | erased status, showing a threshold voltage shift $\Delta V_T$ . $I_{DS}$ , the source-     |    |

|      | drain current; $V_{\rm GS}$ , the gate-source voltage; $V_{\rm REF}$ , the reference       |    |

|      | voltage; $V_{T1}$ , the threshold voltage for erased status; $V_{T2}$ . the                |    |

|      | threshold voltage for programmed status                                                    | 12 |

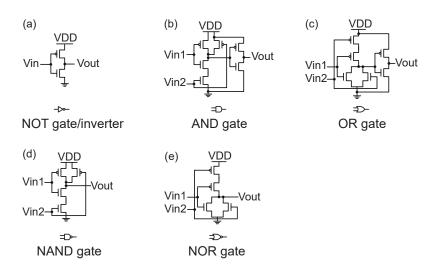

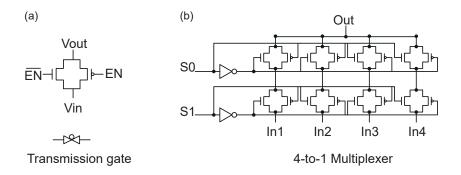

| 2.8  | Instances of CMOS implementation in several two-input logic gates.                         |    |

|      | (a) NOT gate. (b) AND gate. (c) OR gate. (d) NAND gate. (e)                                |    |

|      | NOR gate. Vin, the input voltage; Vout, the output voltage; VDD,                           |    |

|      | the voltage at the drain                                                                   | 13 |

| 2.9  | Circuit diagrams of (a) a transmission gate and (b) a 4-to-1 multi-                        |    |

|      | plexer. Vin, the input voltage; Vout, the output voltage; EN, enable;                      |    |

|      | $\overline{\mathrm{EN}},  \mathrm{disable.}  \ldots \ldots \ldots \ldots$                  | 13 |

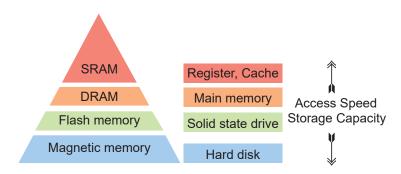

| 2.10 | Pyramid of memory hierarchy. SRAM offers the highest speed with                            |    |

|      | limited capacity while hard disk provides the largest cost-effective                       |    |

|      | capacity in modern PCs                                                                     | 14 |

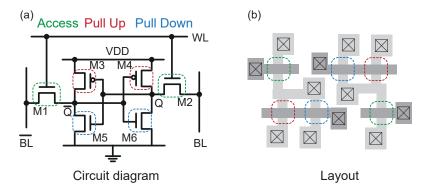

| 2.11 | (a) Transistor configuration and (b) fabrication layout of a 6T SRAM.                      |    |

|      | Data are retained by a pair of inverters in a 6T SRAM [33]. BL, the                        |    |

|      | bitline; $\overline{\mathrm{BL}}$ , the opposite to the BL; VDD, the voltage at the drain. |    |

|      | ${\bf Q}$ and $\overline{\bf Q}$ represent binary values. The checked boxes correspond to  |    |

|      | the contacts                                                                               | 16 |

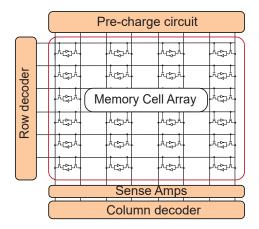

| 2.12 | Generic organisation of SRAM. Information stored in the memory                             |    |

|      | array are addressed and accessed by row and column decoders in two                         |    |

|      | dimensions                                                                                 | 18 |

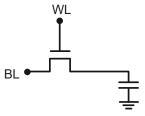

| 2.13 | and BL denote the wordline and the bitline, respectively                                                                                                                           | 19 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

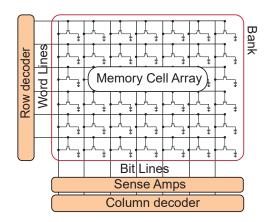

| 2.14 | Schematic diagram of DRAM organisation. DRAM cell array forms a bank where all wordlines and bitlines are addressed and accessed by row and column decoders, respectively          | 20 |

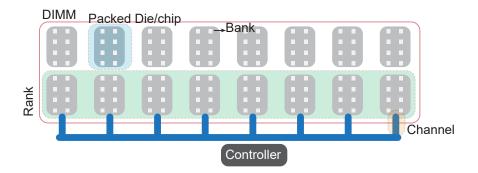

| 2.15 | Schematic of DIMM. Array, bank, rank and DIMM form a hierarchy in the storage organisation                                                                                         | 20 |

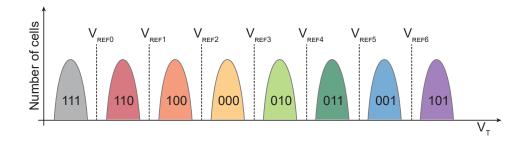

| 2.16 | Illustration of $V_T$ distribution in typical TLC cells and corresponding binary values. $V_T$ , the threshold voltage; $V_{REF}$ , the reference voltage.                         | 21 |

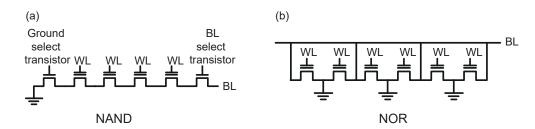

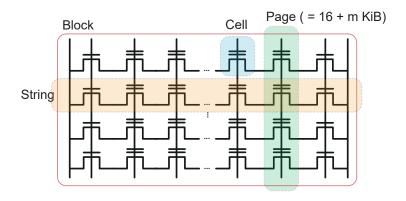

| 2.17 | Sketch of (a) NAND and (b) NOR connections. WL, the wordline; BL, the bitline                                                                                                      | 22 |

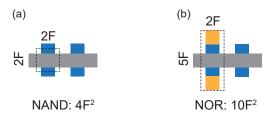

| 2.18 | Typical cell size for (a) NAND and (b) NOR flash in manufacturing, where F stands for the dimension of gate                                                                        | 23 |

| 2.19 | Sketch of NAND flash hierarchy. All cells connected on same bitline form a string while all cells sharing a wordline are in a page                                                 | 24 |

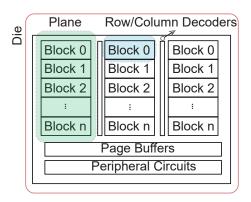

| 2.20 | Organisation of a typical NAND die, indicating internal elements of different levels: block, plane and die                                                                         | 25 |

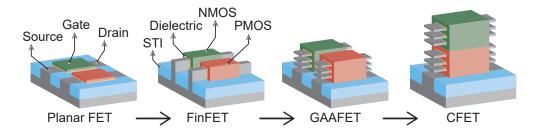

| 2.21 | A schematic representation of the revolution of MOSFET architecture, from planar FET to FinFET, GAAFET and the latest 3D CFET.                                                     | 26 |

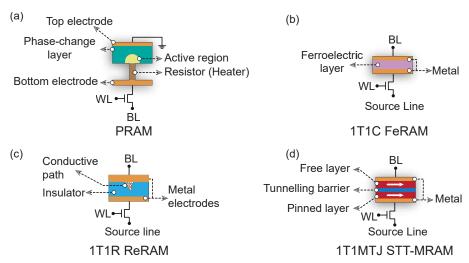

| 2.22 | Memory cell structures for (a) PRAM, (b) FeRAM, (c) ReRAM and (d) STT-MRAM. BL and WL correspond to the bitline and the wordline, respectively                                     | 31 |

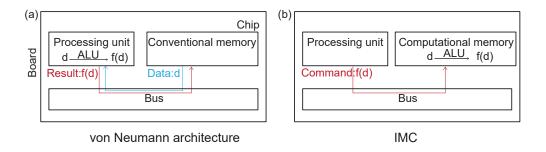

| 2.23 | Illustrative comparison between (a) von Neumann architecture and (b) IMC where the data is processed within the memory unit. ALU stands for the arithmetic-logic unit. d, the data | 35 |

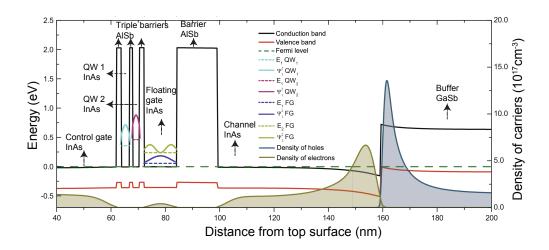

| 2.24 | Calculated band diagram of the first conceptualised ULTRARAM $^{\mathbb{M}}$    |    |

|------|---------------------------------------------------------------------------------|----|

|      | structure. E, the confined energy level; QW, the quantum well; FG,              |    |

|      | the floating gate; $\Psi^2$ , the probability densities for the position of the |    |

|      | electrons in the QWs. The densities of electrons and holes are plotted          |    |

|      | on the right axis [5]                                                           | 38 |

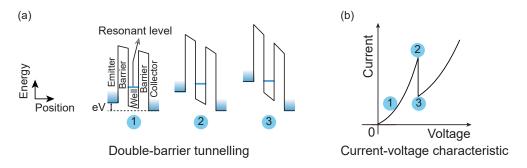

| 2.25 | (a) Band diagram and (b) corresponding positions in I-V character-              |    |

|      | istics of a double-barrier resonant tunnelling structure. The current           |    |

|      | peak in the I-V curve occurs when the emitter level is aligned to the           |    |

|      | quasi-bound level in the quantum well                                           | 39 |

| 2.26 | (a) Band diagram and (b) corresponding positions in I-V characteris-            |    |

|      | tics of a triple-barrier resonant tunnelling structure with asymmetric          |    |

|      | wells. The current peak in the I-V curve occurs when the emitter                |    |

|      | level is aligned to one of the quasi-bound levels in the quantum wells.         | 41 |

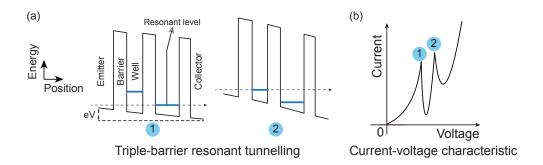

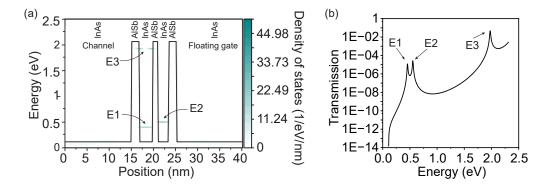

| 2.27 | (a) Density of states as a function of position and (b) transmission            |    |

|      | as a function of energy for primary TBRT design. E1, E2, E3 are                 |    |

|      | resonant levels in the quantum wells                                            | 44 |

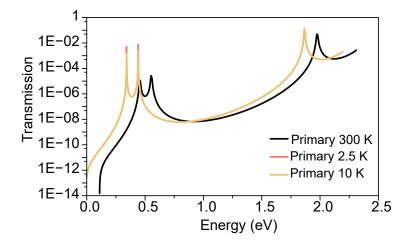

| 2.28 | Simulated transmission of the TBRT structure as a function of energy            |    |

|      | at low temperatures. A higher transmission is observed at a lower               |    |

|      | energy for all resonant peaks                                                   | 45 |

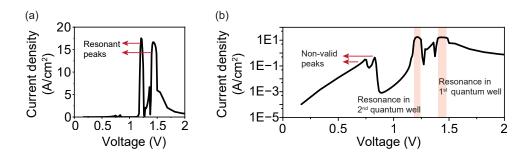

| 2.29 | (a) Linear and (b) logarithmic plot for current-voltage characteristic          |    |

|      | for primary design of the TBRT in forward direction biasing, showing            |    |

|      | resonant peaks with NDR effect. The filled boxes represent the                  |    |

|      | alignments to relevant resonant levels in the quantum wells                     | 46 |

| 2.30 | (a) Linear and (b) logarithmic plot for current-voltage characteristic          |    |

|      | for primary design of the TBRT in reverse direction biasing, showing            |    |

|      | resonant peaks with NDR effect. The filled boxes represent the                  |    |

|      | alignments to relevant reconant levels in the quantum wells                     | 17 |

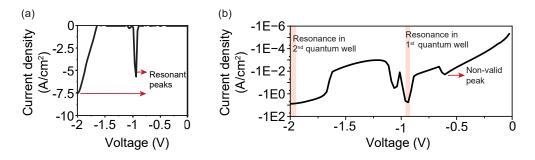

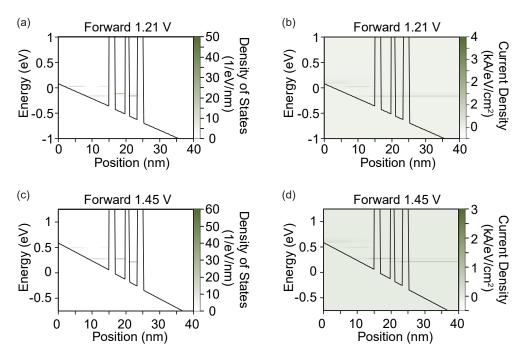

| 2.31 | Simulation plots for two resonance conditions in forward biasing           |    |

|------|----------------------------------------------------------------------------|----|

|      | direction. (a) Density of states and (b) current density at 1.21 V.        |    |

|      | (c) Density of states and (d) current density at 1.45 V                    | 48 |

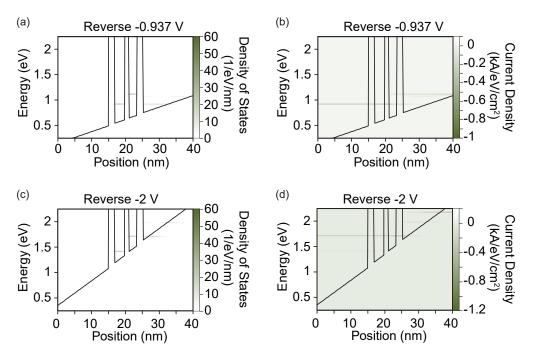

| 2.32 | Simulation plots for two resonance conditions in reverse biasing           |    |

|      | direction. (a) Density of states and (b) current density at -0.937         | 40 |

|      | V. (c) Density of states and (d) current density at -2 V                   | 49 |

| 2.33 | (a) Diagram of band structures of InAs and (b) its {001}, {110}            |    |

|      | surfaces of zinc blende lattice. The grey box outlines the conventional    |    |

|      | unit cell                                                                  | 51 |

| 2.34 | (a) Illustration of ULTRARAM <sup>TM</sup> structure and (b) plot of III-V |    |

|      | compounds energy gap as a function of lattice constant [224]               | 52 |

| 3.1  | Simplified schematic of an MBE growth. Elements from effusion cells        |    |

|      | are sequentially controlled to be deposited onto the target substrate      |    |

|      | in a high vacuum condition with RHEED monitoring the real-time             |    |

|      | thickness                                                                  | 55 |

| 3.2  | Illustration of (a) Frank-van der Merwe growth mode, (b) Volmer-           |    |

|      | Weber growth mode and (c) Stranski-Krastanov growth mode                   | 56 |

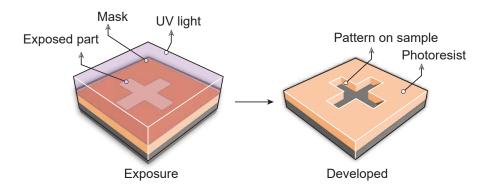

| 3.3  | Schematic of an optical mask lithography process with mask aligner.        |    |

|      | The sample covered by photoresist is first in touch with mask and then     |    |

|      | exposed to UV light, the pattern is transferred onto the developed         |    |

|      | sample after developing process                                            | 57 |

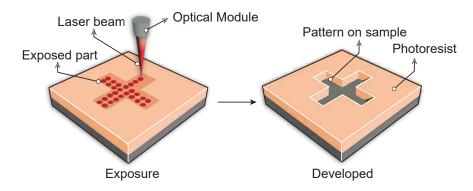

| 3.4  | Schematic of lithography done with an LW. The pattern region to            |    |

|      | be exposed is scanned by a moving laser spot, then the pattern is          |    |

|      | transferred onto the sample after developing procedure                     | 58 |

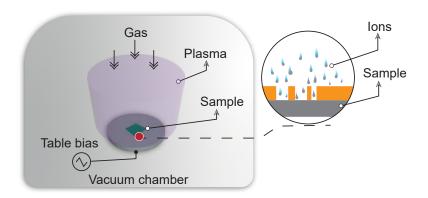

| 3.5  | Illustration of RIE etching. The reactive ions are dragged onto            |    |

|      | the substrate by table bias to sputter or chemically react with            |    |

|      | the uncoated regions on the sample to reproduce the pattern from           |    |

|      | lithography.                                                               | 60 |

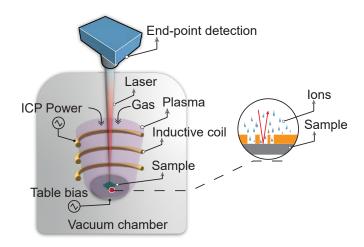

| 3.6 | Illustration of ICP etching with end-point detection technique. The                        |       |

|-----|--------------------------------------------------------------------------------------------|-------|

|     | introduction of the coil contributes to higher etch rate. The laser                        |       |

|     | interferometry shines and collects reflected light to make real-time                       |       |

|     | etching control feasible                                                                   | 61    |

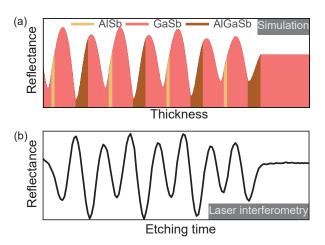

| 3.7 | Comparison between (a) simulated reflectances and (b) data obtained                        |       |

|     | from laser interferometry of a periodic GaSb/AlSb/GaSb/AlGaSb                              |       |

|     | structure. The simulation is done at 670 nm, the same wavelength                           |       |

|     | used in the laser interferometry: the two curves show good matching                        |       |

|     | in terms of the number of peaks and general shape                                          | 63    |

|     |                                                                                            |       |

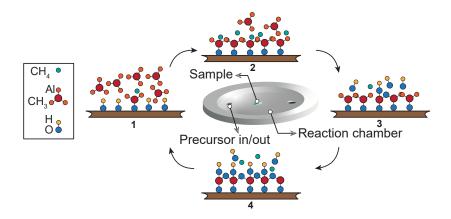

| 3.8 | Schematic representation of the sequential ALD process for ${\rm Al_2O_3}$                 |       |

|     | growth. In step 1, the $\mathrm{Al}(\mathrm{CH}_3)_3$ precursor is pumped into the chamber |       |

|     | and absorbed by hydroxyl on the surface. The reaction produces                             |       |

|     | CH <sub>4</sub> . This is a self-limiting reaction as the precursor does not react         |       |

|     | with absorbed Al species. In step 2, the reaction products and un-                         |       |

|     | reacted precursor are removed from the chamber by flowing inert                            |       |

|     | gas to prepare the top surface for next process. In step 3, ${\rm H_2O}$ is                |       |

|     | introduced to the deposited methyl surface. The reaction creates the                       |       |

|     | Al-O-Al bridge and leaves new hydroxyl on surface. $\mathrm{CH}_4$ is released as          |       |

|     | a by-product. In step 4, a same removal process for reaction products                      |       |

|     | and un-reacted precursor. Repeat the four steps again to grow an                           |       |

|     | alumina layer with desired thickness. Due to the self-limiting process,                    |       |

|     | only one layer of alumina is grown after each cycle                                        | 65    |

| 2.0 | Illustration of a DECVD sharehor Desertant research initial Co                             |       |

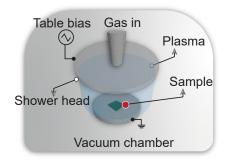

| 3.9 | Illustration of a PECVD chamber. Reactant gases are injected from                          |       |

|     | an engineered shower head and then react near the substrate to                             | 66    |

|     | DIOGRAM HILLIERS                                                                           | 1 ) ( |

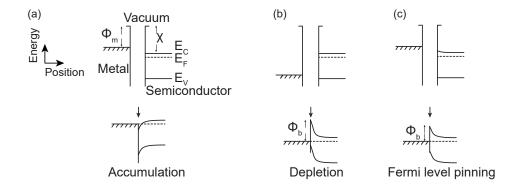

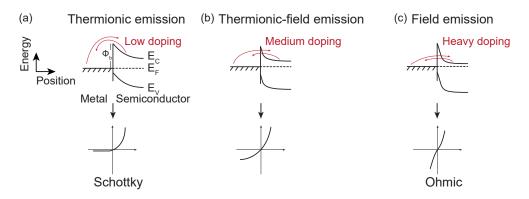

| 3.10   | Band diagrams of three contact types with instance of an interface                            |      |

|--------|-----------------------------------------------------------------------------------------------|------|

|        | between a metal and an n-type semiconductor. (a) Accumulation. No                             |      |

|        | contact barrier is formed at the interface between the metal and the                          |      |

|        | n-type semiconductor when $\Phi_{\rm m} < X$ and electrons are accumulated                    |      |

|        | at the interface due to band bending. (b) Depletion. Electrons are                            |      |

|        | depleted due to band bending when $\Phi_{\rm m}>X$ and the Schottky barrier                   |      |

|        | can be calculated by $\Phi_{\rm b}$ = $\Phi_{\rm m}$ - X. (c) Fermi level pinning. The        |      |

|        | bands in the semiconductor bend before in contact due to surface                              |      |

|        | states. The bands bend again after in touch with metal, followed by                           |      |

|        | a contact barrier created at the surface. The barrier is caused by the                        |      |

|        | metal induced gap states at the surface of the semiconductor, and                             |      |

|        | the barrier height is independent of the metal work function. $\Phi_{\rm m},$ the             |      |

|        | metal work function; X, the electron affinity; $\Phi_b$ , the barrier height;                 |      |

|        | $E_{\rm C},$ the conduction band; $E_{\rm F},$ the Fermi level; $E_{\rm V},$ the valence band | 68   |

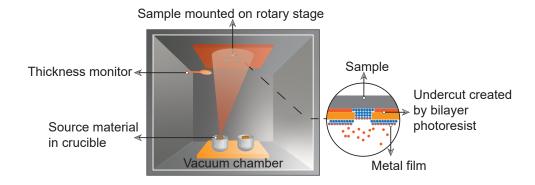

| 3.11   | Diagram of a thermal evaporation process. The metal is vaporized                              |      |

|        | by resistive heating and then reconstructs on the sample surface to                           |      |

|        | accomplish film deposition                                                                    | 69   |

| 3.12   | Three conduction mechanisms for metal-semiconductor interfaces of                             |      |

|        | various barriers and corresponding I-V characteristics. (a) Thermionic                        |      |

|        | emission. (b) Thermionic-field emission. (c) Field emission. Higher                           |      |

|        | doping level shapes a more linear I-V curve. $\Phi_{\rm b}$ , the barrier height;             |      |

|        | $E_{\rm C},$ the conduction band; $E_{\rm F},$ the Fermi level; $E_{\rm V},$ the valence band | 70   |

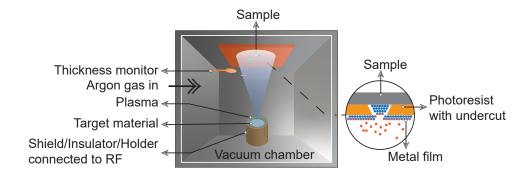

| 3.13   | Illustration of a sputterer chamber. Sputtered metal atoms with high                          |      |

|        | energy hit the sample surface to form a film                                                  | 71   |

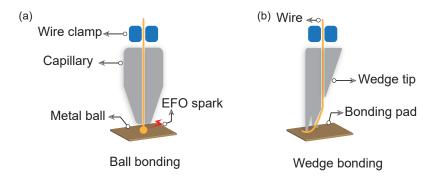

| 3.14   | Schematic representation of two types of wire bonding, highlighting                           |      |

|        | details of the difference between the tips. (a) Ball bonding. (b) Wedge                       |      |

|        | bonding                                                                                       | 72   |

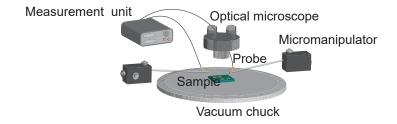

| 3.15   | Schematic representation of components in a typical probe station                             |      |

| J. 1 U | set-up for electrical measurement                                                             | 74   |

|        | see up for electrical incapatement                                                            | 1 -1 |

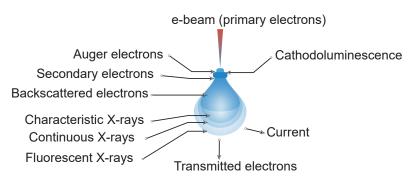

| 3.16 | Schematic representation of the beam-specimen interaction, showing                    |    |

|------|---------------------------------------------------------------------------------------|----|

|      | various signals that can be collected and analysed                                    | 76 |

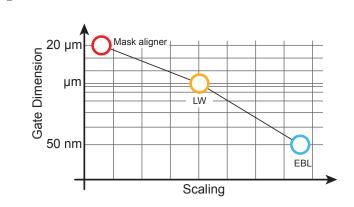

| 4.1  | Sketch of the scaling route for ULTRARAM $^{\text{\tiny TM}}$ memory                  | 81 |

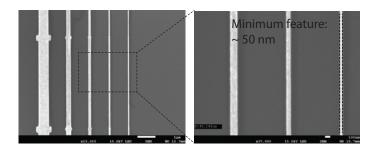

| 4.2  | SEM images of a group of EBL patterned metal bars, showing the                        |    |

|      | achieved minimum feature size $\sim 50$ nm                                            | 81 |

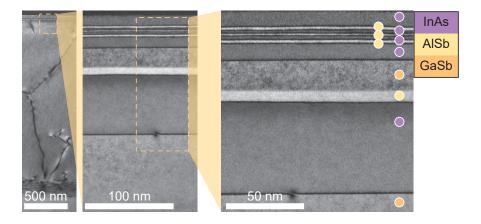

| 4.3  | Cross-sectional TEM images of different scales of XPH 1452 wafer,                     |    |

|      | presenting high quality of III-V memory layers. The coloured dots                     |    |

|      | denote the corresponding materials in the legend. Images provided                     |    |

|      | with permission from Dr Richard Beanland, University of Warwick                       | 84 |

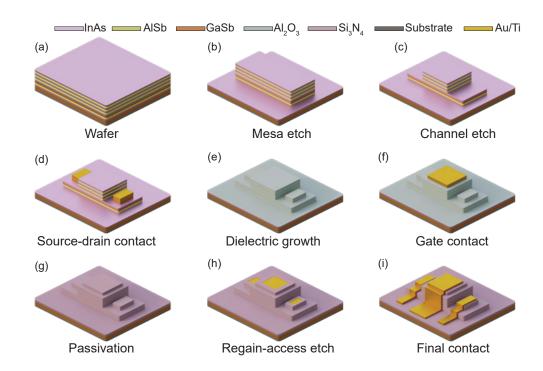

| 4.4  | Simplified illustration of fabrication steps for wet-etching design that              |    |

|      | requires five alignments. (a) Wafer preparation. (b) Mesa etch. (c)                   |    |

|      | Channel etch. (d) Source-drain contact formation. (e) Dielectric                      |    |

|      | growth. (f) Gate contact deposition. (g) Passivation layer deposition.                |    |

|      | (h) Regain access etch. (i) Final contact formation                                   | 85 |

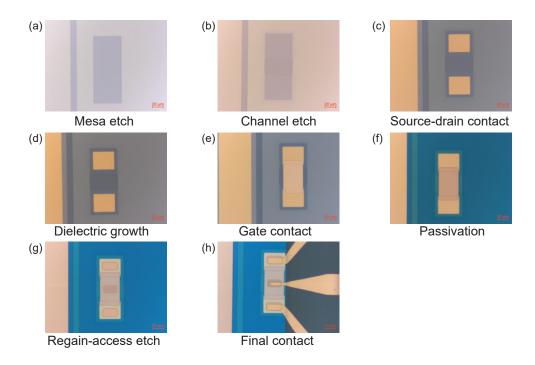

| 4.5  | Optical photos from each step in the fabrication using the wet-etch                   |    |

|      | design. (a) Mesa etch. (b) Channel etch. (c) Source-drain contact                     |    |

|      | formation. (d) Dielectric growth. (e) Gate contact deposition. (f)                    |    |

|      | Passivation layer deposition. (g) Regain access etch. (h) Final contact               |    |

|      | formation                                                                             | 87 |

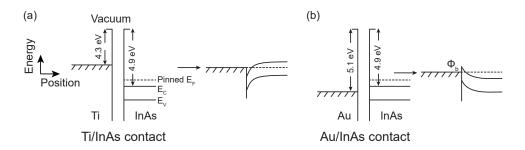

| 4.6  | Simplified band diagram of (a) Ti and (b) Au contact to InAs channel.                 |    |

|      | A Schottky barrier occurs for the use of gold. E <sub>F</sub> , the Fermi level;      |    |

|      | $E_C$ , the conduction band; $E_V$ , the valence band; $\Phi_b$ , the barrier height. | 88 |

| 4.7  | Comparison between (a) wet etching and (b) dry etching. Dry etching                   |    |

|      | is more directional                                                                   | 90 |

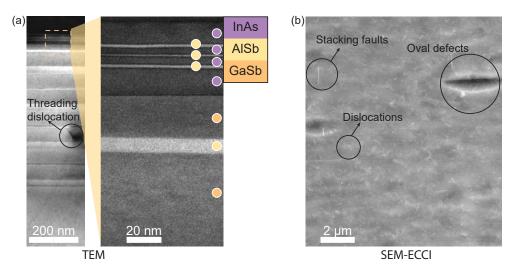

| 4.8  | (a) Cross-sectional TEM images at different scales and (b) SEM-                       |    |

|      | ECCI image of XPH 1823 wafer, presenting the vertical structures and                  |    |

|      | surface condition of as-grown wafer, respectively. The coloured dots                  |    |

|      | denote the corresponding materials in the legend. Images provided                     |    |

|      | with permission from Dr Richard Beanland, University of Warwick                       | 92 |

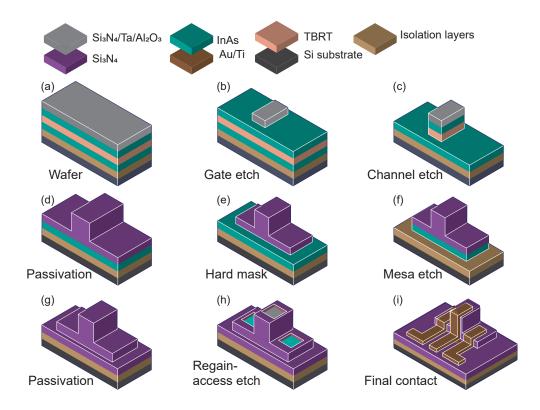

| 4.9  | Schematic representation of the self-aligned design with fabrication                 |    |

|------|--------------------------------------------------------------------------------------|----|

|      | steps. (a) Hard mask layers deposition on wafer. (b) Gate definition                 |    |

|      | etch. (c) Self-aligned channel access etch. (d) Passivation with $\mathrm{Si_3N_4}.$ |    |

|      | (e) Hard mask definition etch. (f) Self-aligned mesa etch. (g) Second                |    |

|      | passivation layer. (h) Regain access etch. (i) Final contact formation.              | 93 |

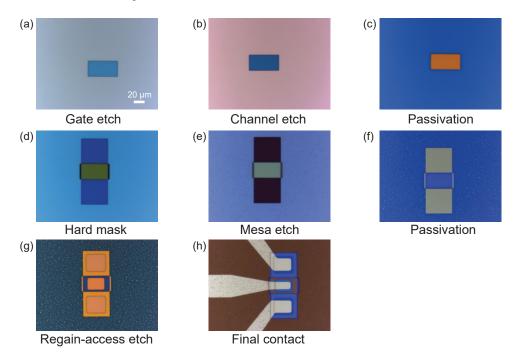

| 4.10 | Fabrication photos of each step in the self-aligned design. (a) Gate                 |    |

|      | definition etch. (b) Self-aligned channel access etch. (c) Passivation               |    |

|      | with $\mathrm{Si_3N_4}$ . (d) Hard mask definition etch. (e) Self-aligned mesa       |    |

|      | etch. (f) Second passivation layer. (g) Regain access etch. (h) Final                |    |

|      | contact formation                                                                    | 94 |

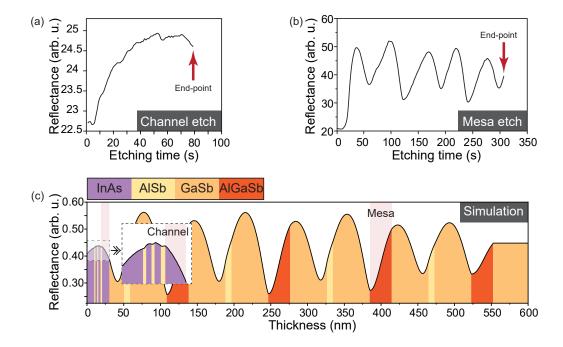

| 4.11 | Etching reflectances from the fabrication for (a) channel etching and                |    |

|      | (b) mesa etching, as a comparison to reference regions indicated in                  |    |

|      | (c) simulated curves. The inset in (c) shows the zoom-in of the TBRT                 |    |

|      | and channel region                                                                   | 95 |

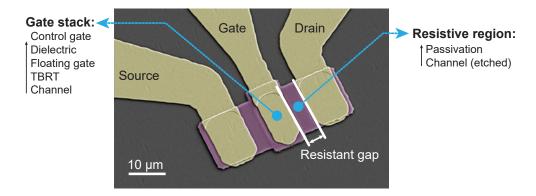

| 4.12 | Coloured SEM image of a device fabricated with self-aligned design,                  |    |

|      | a gap is shown between the gate stack and the source/drain contact.                  |    |

|      | The resistant gap of micron scale originates from the device design.                 |    |

|      | Layer arrangements for the gate stack and the resistive region are                   |    |

|      | listed on both sides of the image. The gold colour denotes the                       |    |

|      | region covered by contact metal and the magenta region represents                    |    |

|      | the surface covered by passivation $Si_3N_4$                                         | 97 |

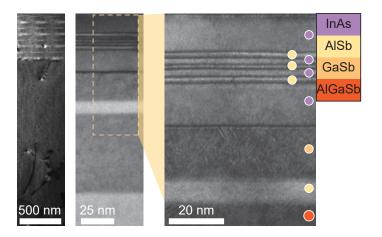

| 4.13 | Cross-sectional TEM images at different scales of the XPH 2318                       |    |

|      | wafer. The coloured dots denote the corresponding materials in the                   |    |

|      | legend. Images provided with permission from Dr Richard Beanland,                    |    |

|      | University of Warwick.                                                               | 99 |

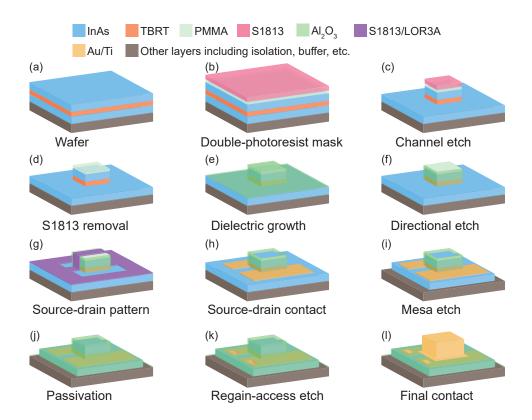

| 4.14 | Schematic representation of the improved design with fabrication                               |

|------|------------------------------------------------------------------------------------------------|

|      | steps. (a) Wafer preparation. (b) Mask-photoresist spin-coating. (c)                           |

|      | Channel etching. (d) Top S1813 photoresist removal. (e) Dielectric                             |

|      | growth. (f) Anisotropic etching of the dielectric. (g) Source-drain                            |

|      | contact patterning. (h) Source-drain contact formation. (i) Mesa                               |

|      | etch. (j) Passivation layer deposition. (k) Regain access etch. (l)                            |

|      | Final contact formation                                                                        |

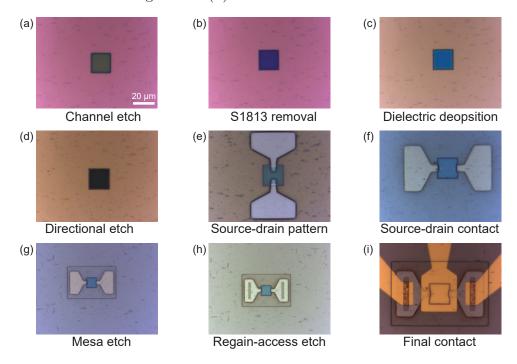

| 4.15 | Fabrication photos of each step using the improved design. (a)                                 |

|      | Channel etching. (b) Top S1813 photoresist removal. (c) Dielectric                             |

|      | growth. (d) Anisotropic etching of the dielectric. (e) Source-drain                            |

|      | contact patterning. (f) Source-drain contact formation. (g) Mesa                               |

|      | etch. (h) Regain access etch. (i) Final contact formation                                      |

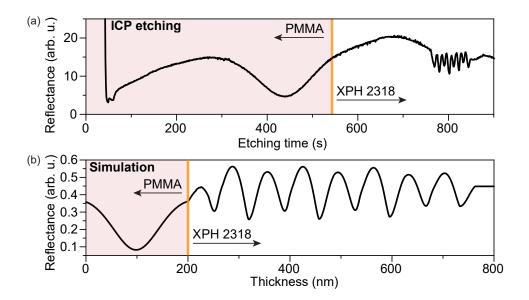

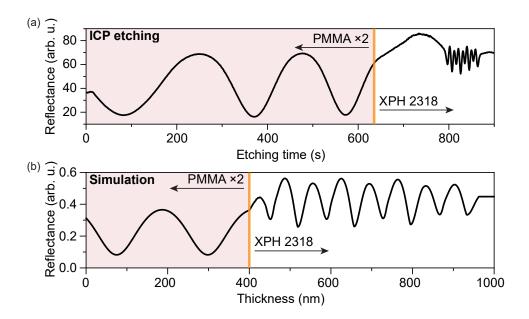

| 4.16 | (a) Etching reflectance from the etch-through of PMMA/XPH 2318                                 |

|      | structure. (b) The simulation for the structure in (a). Reflectance                            |

|      | fingerprints of the PMMA are superimposed on the beginning of the                              |

|      | known wafer reflectance. The orange line marks the stop line for end-                          |

|      | point detection. Double layers of PMMA were used in the etching                                |

|      | with a nominal thickness of 200 nm, which was used for the simulation                          |

|      | in (b). The deviation between (a) and (b) can be attributed to the                             |

|      | variation of PMMA thickness which depends on the spinning and                                  |

|      | baking conditions. The initial drop was caused by focus adjustment                             |

|      | at the beginning of the etch due to signal issue                                               |

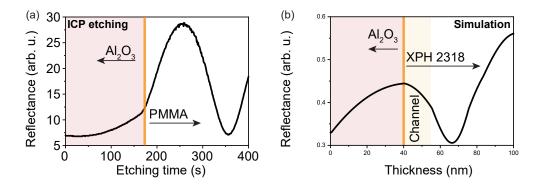

| 4.17 | (a) Etching reflectance from the etching of $\mathrm{Al_2O_3/PMMA/XPH}$                        |

|      | 2318 structure. (b) The simulation for $\mathrm{Al_2O_3/Channel/Other}$ layers                 |

|      | beneath the channel from XPH 2318 structure. The orange line marks                             |

|      | the stop line for end-point detection. 40-nm thick Al <sub>2</sub> O <sub>3</sub> was used for |

|      | the simulation                                                                                 |

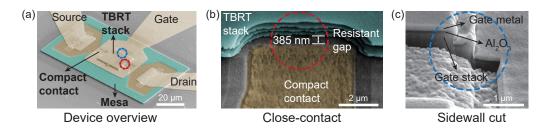

| 4.18 | (a) Colourized SEM image of an as-fabricated device with improved           |     |

|------|-----------------------------------------------------------------------------|-----|

|      | design. The green region outlines the exposed mesa area while gold          |     |

|      | colour indicates the top electrodes. (b) Zoom-in image of the red-          |     |

|      | circled region in (a), showing a reduced resistive gap of around 380        |     |

|      | nm. The green filled region denotes the TBRT stack while the gold           |     |

|      | colour region represents the compact source-drain contact. (c) The          |     |

|      | FIB cut at gate stack region as indicated by blue circle in (a), showing    |     |

|      | a high-quality sidewall                                                     | 104 |

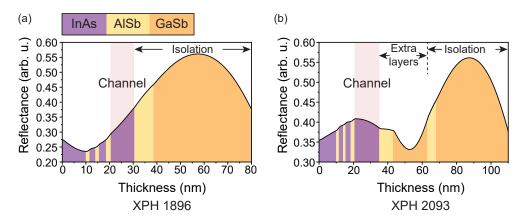

| 4.19 | Simulations of reflectance for (a) XPH 1896 and (b) XPH 2093 at             |     |

|      | 670 nm wavelength, the additional AlSb/GaSb can be used as an               |     |

|      | over-etching signal                                                         | 106 |

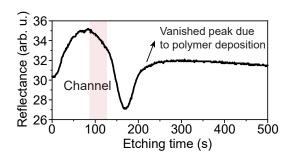

| 4.20 | A reflectance from the mesa etching of a fabrication on XPH 1823            |     |

|      | wafer using CH <sub>4</sub> -based recipe, showing a narrow time window and |     |

|      | the flattened signal caused by the polymer deposition                       | 107 |

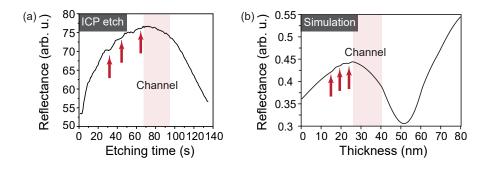

| 4.21 | (a) Best ICP etching from XPH 2213 using the optimised recipe,              |     |

|      | showing clear matching with (b) unique features of the TBRT in the          |     |

|      | simulation                                                                  | 107 |

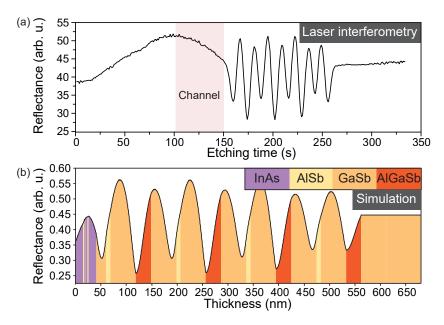

| 4.22 | (a) Etch-through reflectance of XPH 2318 wafer with its reference to        |     |

|      | (b) the simulation of the same structure                                    | 108 |

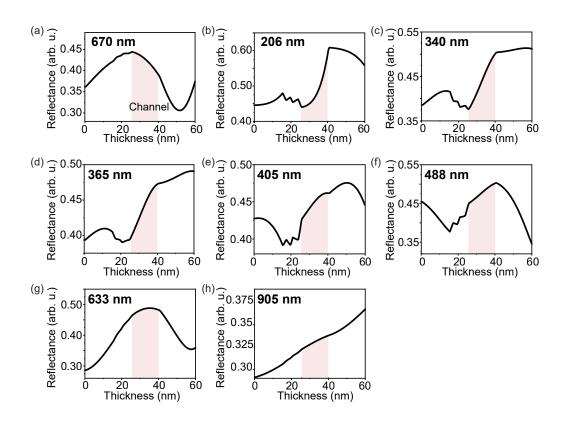

| 4.23 | Simulated etching reflectances for various wavelengths at room tem-         |     |

|      | perature with focus on the TBRT region, fine features of InAs/AlSb          |     |

|      | get a higher contrast at shorter wavelengths while being flattened at       |     |

|      | longer wavelengths. The red boxes mark the channel region in each           |     |

|      | curve. (a) 670 nm. (b) 206 nm. (c) 340 nm. (d) 365 nm. (e) 405 nm.          |     |

|      | (f) 488 nm. (g) 633 nm. (h) 905 nm                                          | 111 |

|      | · · · · · · · · · · · · · · · · · · ·                                       |     |

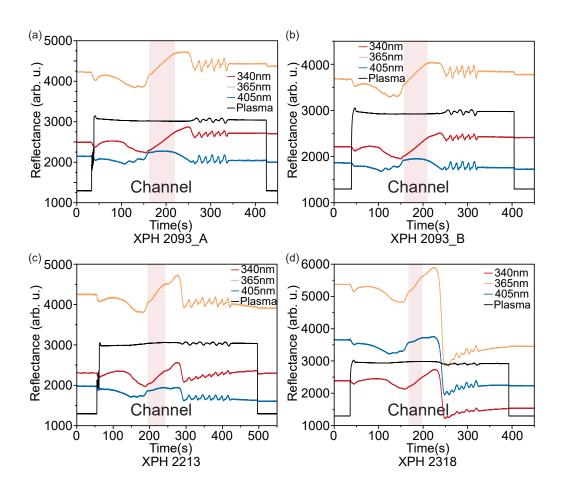

| 4.24 | Reflectances of etch-through on samples including (a) XPH 2093_A,                                                      |       |

|------|------------------------------------------------------------------------------------------------------------------------|-------|

|      | (b) XPH 2093_B, (c) XPH 2213 and (d) XPH 2318 acquired using                                                           |       |

|      | three wavelengths of $340$ nm, $365$ nm and $405$ nm, showing the                                                      |       |

|      | consistency of fingerprint features of the TBRT across various designs. $$                                             |       |

|      | The etching and data collection were done in collaboration with David                                                  |       |

|      | Cornwell, LayTec AG                                                                                                    | . 112 |

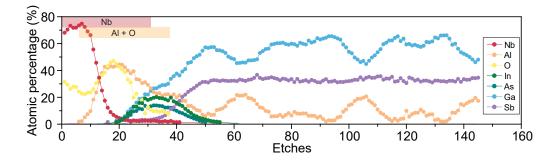

| 5.1  | XPS characterisation of multiple layers on XPH 1896 wafer. XPS                                                         |       |

|      | signals are collected and analysed after each run of milling down with                                                 |       |

|      | a certain amount of the thickness. The Nb signal overlapping with                                                      |       |

|      | the combination of Al and O signals shows the diffusion of Nb into                                                     |       |

|      | dielectric layer. The percentage numbers are indicative                                                                | . 116 |

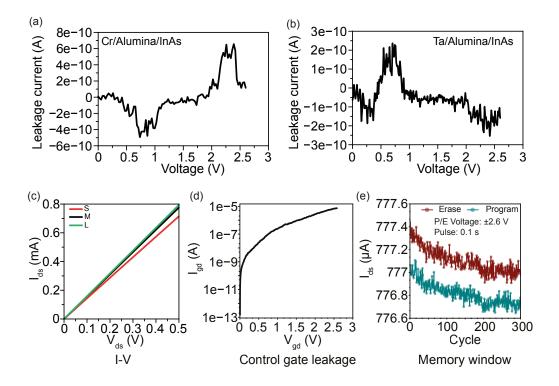

| 5.2  | Leakage test for (a) Cr and (b) Ta on alumina. (c) I-V curves for                                                      |       |

|      | devices with gate size S, M and L. The gate dimensions of S, M and                                                     |       |

|      | L are $10.5 \times 20~\mu\text{m}^2$ , $25 \times 30.5~\mu\text{m}^2$ and $30 \times 56~\mu\text{m}^2$ , respectively. |       |

|      | (d) Gate leakage and (e) memory window plot of the memory device                                                       |       |

|      | of size M in (a) from XPH 1823 using $\mathrm{Si_3N_4}$ as mask for gate definition                                    | ı.117 |

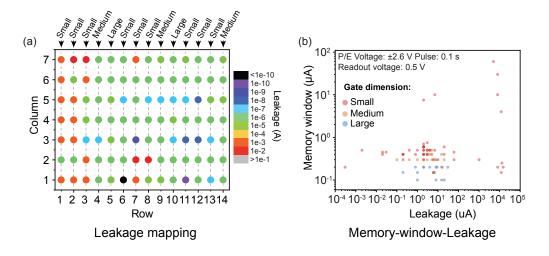

| 5.3  | (a) Leakage mapping and (b) memory-window-leakage plot of the                                                          |       |

|      | fabrication from XPH 1823 using $\mathrm{Si_3N_4}$ as mask for gate definition.                                        |       |

|      | The device positioned in the first column of the sixth row is non-                                                     |       |

|      | functional                                                                                                             | . 118 |

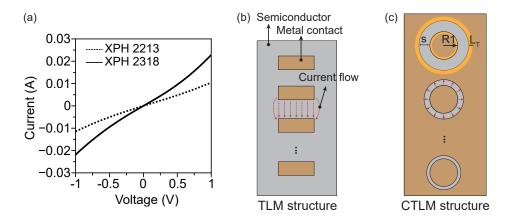

| 5.4  | (a) I-V measurement of samples from XPH 2213 and XPH 2318 under                                                        |       |

|      | same etching conditions. (b) TLM and (c) CTLM structure. The                                                           |       |

|      | dashed arrows in (a) shows the current crowding which causes the                                                       |       |

|      | current to flow through other sides of the pad. s, the gap between                                                     |       |

|      | inner electrode and common ground; R1, the radius of inner electrode;                                                  |       |

|      | $L_T$ , the transfer length                                                                                            | . 120 |

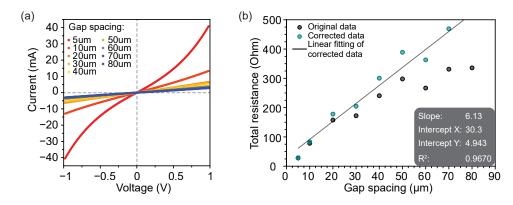

| 5.5  | (a) I-V measurement data for CTLM and (b) CTLM analysis of                                                             |       |

|      | XPH 2318 wafer. Nine different gap spacings were used in the                                                           |       |

|      | characterisation, R <sup>2</sup> , the coefficient of determination,                                                   | . 122 |

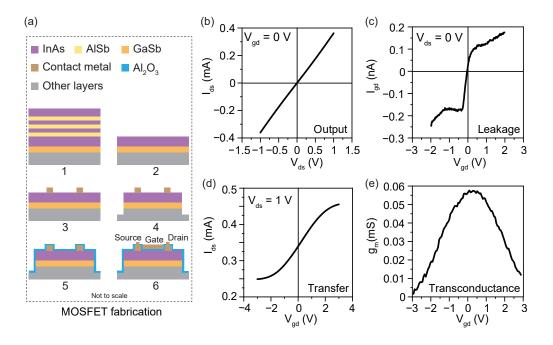

| 5.6  | <ul> <li>(a) MOSFET fabrication steps for the measurement.</li> <li>(b) Output,</li> <li>(c) leakage,</li> <li>(d) transfer and</li> <li>(e) transconductance characteristics of</li> <li>a MOSFET device fabricated on XPH 2318.</li> <li>I<sub>ds</sub>, the source-drain</li> </ul>                                                                                                                                                                                                                                            |       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|      | current; $V_{ds}$ , the source-drain voltage; $I_{gd}$ , the gate-drain current; $V_{ds}$ , the gate-drain voltage; $g_m$ , the transconductance                                                                                                                                                                                                                                                                                                                                                                                  | . 124 |

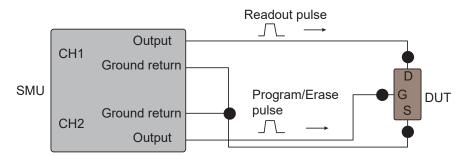

| 5.7  | Schematic of measurement connections in a typical ULTRARAM $^{\text{TM}}$ memory test. CHn, the measurement channel; G, the device gate terminal; D, the device drain terminal; S, the device source terminal; DUT, the device under test                                                                                                                                                                                                                                                                                         | . 126 |

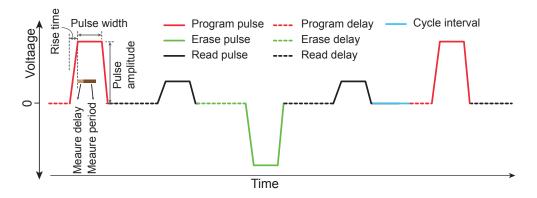

| 5.8  | Pulse pattern for memory endurance characterisation, showing a multiple-level pulse waveform                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 127 |

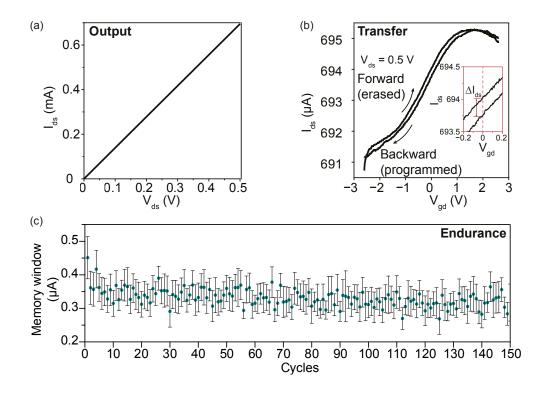

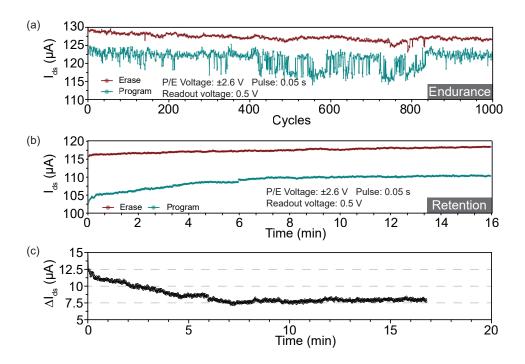

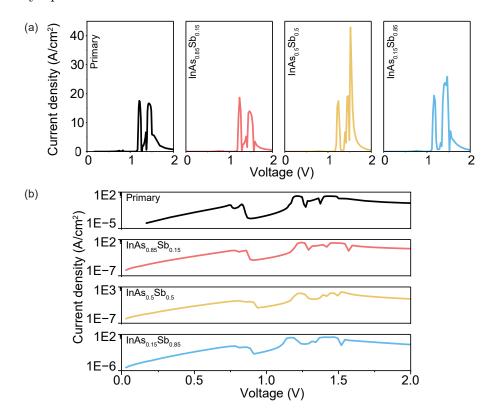

| 5.9  | (a) Output, (b) transfer sweep and (c) endurance memory window as a function of switching cycles for devices from XPH 1823 with a readout voltage of 0.5 V. Endurance data are shown as mean $\pm$ standard error from multiple devices. The inset in (b) depicts the current discrepancy $\Delta I_{ds}$ at zero gate bias which implies the existence of charges stored in the floating gate for programmed status. $I_{ds}$ , the source-drain current; $V_{ds}$ , the source-drain voltage; $V_{gd}$ , the gate-drain voltage | . 129 |

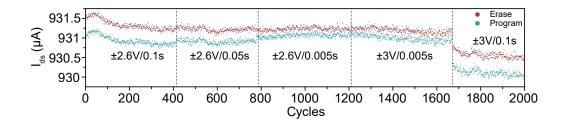

| 5.10 | Endurance characterisation at various voltages and pulse widths of a device from fabrication on XPH 1823. $I_{ds}$ , the source-drain current. $\pm 2.6~V/0.1~s$ denotes the memory operation voltage $\pm 2.6~V$ with a pulse duration of 0.1 s, this convention applies similarly to all subsequent annotations. Readout voltage is set to 0.5 V for all measurements                                                                                                                                                           | 121   |

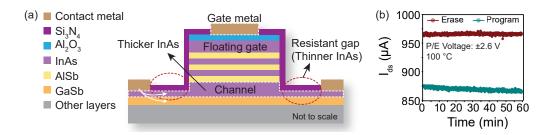

| 5.11 | (a) Cross-section sketch of the device fabricated with self-aligned                  |

|------|--------------------------------------------------------------------------------------|

|      | design, showing drawbacks of native resistive gap. The gate metal                    |

|      | is smaller than the floating gate, so there is limited gate control over             |

|      | channel region. (b) Retention test at 100 °C. The P/E voltage was                    |

|      | achieved by a half voltage scheme with $+$ 1.3 V applied on the source               |

|      | and - 1.3 V applied on the drain. The high temperature measurement                   |

|      | was performed by Charlie Senior and Max Walker Long 132                              |

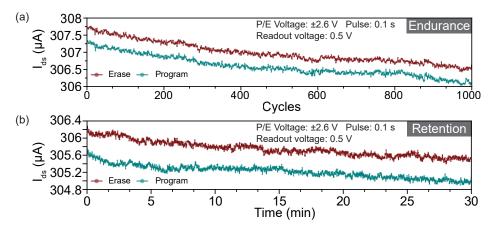

| 5.12 | (a) Endurance, (b) retention and (c) retention memory window of                      |

|      | a memory device from fabrication on XPH 2213, showing a stable                       |

|      | memory window of 5 $\mu A.$ $I_{ds},$ the source-drain current; $\Delta I_{ds},$ the |

|      | retention memory window                                                              |

| 5.13 | (a) Endurance and (b) retention characterisations of a memory device                 |

|      | from fabrication on XPH 2318, showing a stable memory window of                      |

|      | 0.5 $\mu$ A. $I_{ds}$ , the source-drain current                                     |

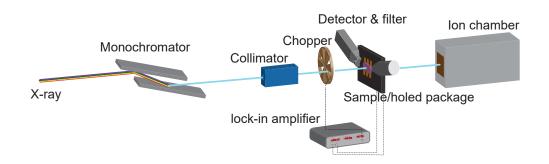

| 5.14 | Illustration of set-up for XANES measurement                                         |

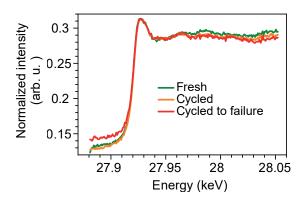

| 5.15 | XANES curves of fresh, cycled and cycled to failure devices under                    |

|      | In K-edge energy set-up, no evidence of In-related defects to cycling                |

|      | failure                                                                              |

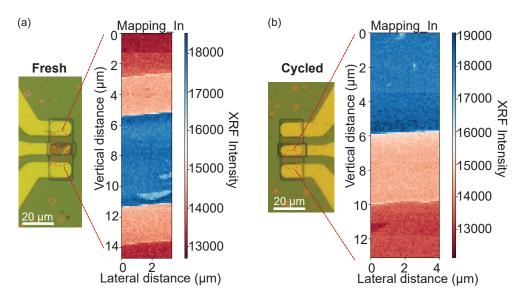

| 5.16 | XRF mappings of (a) fresh and (b) cycled devices from XPH 1896                       |

|      | under In K-edge energy set-up, no significant difference is observed                 |

|      | between fresh and cycled devices. The lateral and vertical distances                 |

|      | correspond to the dimensions scanned, as indicated by dash boxes on                  |

|      | device photos to the left of each mapping                                            |

| 6.1  | (a) Cross-section TEM of TBRT layers of XPH 2093 wafer. InAs                         |

|      | and AlSb layers are denoted on top and bottom of the figure. (b)                     |

|      | Compositional analysis of corresponding layers of the TBRT in (a).                   |

|      | Images provided with permission from Professor Richard Beanland,                     |

|      | University of Warwick                                                                |

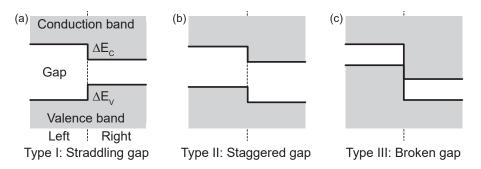

| 6.2 | Schematic representations of three band alignment types. (a) Straddling gap. (b) Staggered gap. (c) Broken gap. $\Delta E_C$ , the |

|-----|------------------------------------------------------------------------------------------------------------------------------------|

|     | conduction band offset; $\Delta E_V$ , the valence band offset                                                                     |

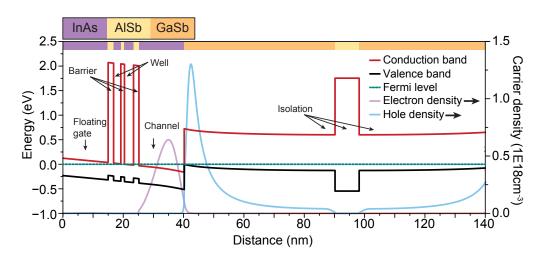

| 6.3 | Calculated band profile of the epitaxial design of XPH 2318 at $300$                                                               |

|     | K. Corresponding layers are denoted by colour boxes on the top.                                                                    |

|     | Electron and hole density are plotted on the right Y-axis                                                                          |

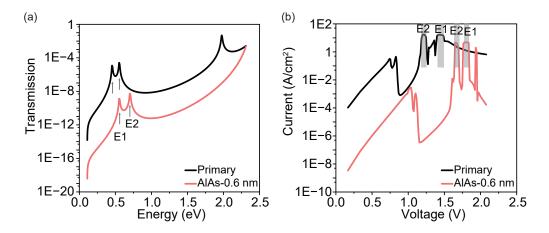

| 6.4 | (a) Primary design and (b) AlAs-0.6 nm layer configuration used for                                                                |

|     | the TBRT simulation                                                                                                                |

| 6.5 | (a) Transmission and (b) current-voltage characteristic for the in-                                                                |

|     | terface alloying with insertion of a 0.6-nm AlAs layer, showing                                                                    |

|     | raised resonant levels and reduced transmission coefficient and current                                                            |

|     | intensity. The grey boxes in (b) correspond to the alignments of two                                                               |

|     | resonant levels in (a)                                                                                                             |

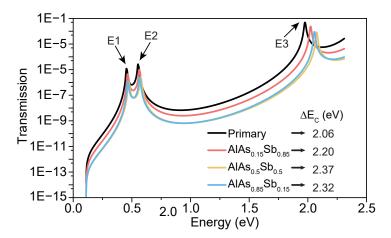

| 6.6 | Transmission through the TBRT with varying AlSb barrier alloying                                                                   |

|     | as a function of energy. The higher As fraction in the barrier pushes                                                              |

|     | resonant levels slightly higher. $\Delta E_{\rm C},$ the conduction band offset. E1,                                               |

|     | E2 and E3 are three resonant levels                                                                                                |

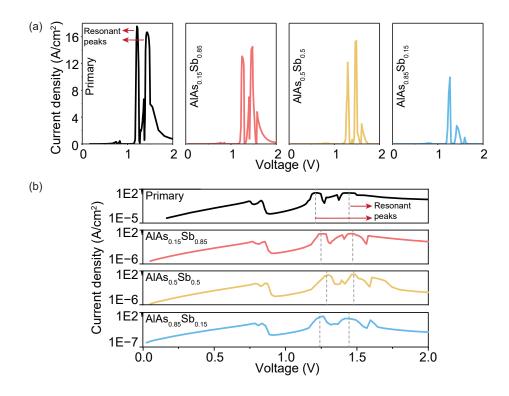

| 6.7 | (a) Linear and (b) logarithmic plot for current-voltage characteristics                                                            |

|     | of the TBRT with varying AlSb barrier alloying as a function of                                                                    |

|     | energy, showing limited changes from As incorporation into AlSb layers. $150$                                                      |

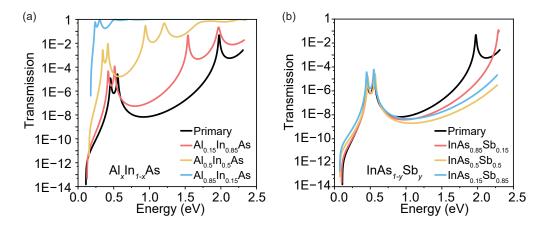

| 6.8 | Transmission of the TBRT with varying InAs quantum well alloying                                                                   |

|     | as a function of energy for (a) $Al_xIn_{1-x}As$ and (b) $InAs_{1-y}Sb_y$ .                                                        |

|     | Al fractional composition higher than 0.5 leads to a decaying                                                                      |

|     | transmission while Sb alloying into InAs has a limited effect on the                                                               |

|     | first two resonant levels                                                                                                          |

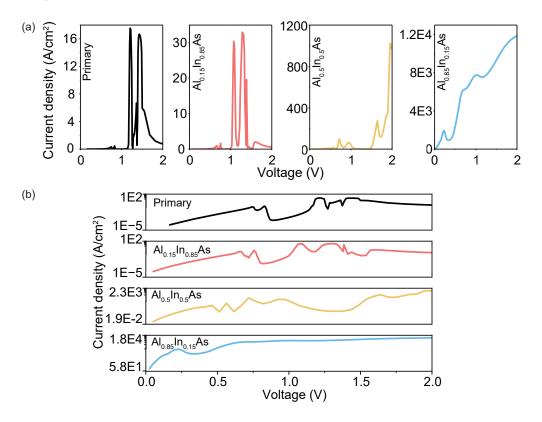

| 6.9  | (a) Linear and (b) logarithmic plot for current-voltage characteristics of the TBRT with varying InAs quantum well alloying as a function of energy for $\mathrm{Al}_x\mathrm{In}_{1-x}\mathrm{As}$ . The degradation of the resonant peaks                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|      | suggests the disappearance of the charge blocking capability of the TBRT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 152 |

| 6.10 | (a) Linear and (b) logarithmic plot for current-voltage characteristics of the TBRT with varying InAs quantum well alloying as a function of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

|      | energy for $\text{InAs}_{1-y}\text{Sb}_y$ . No significant impact from Sb incorporation is observed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 153 |

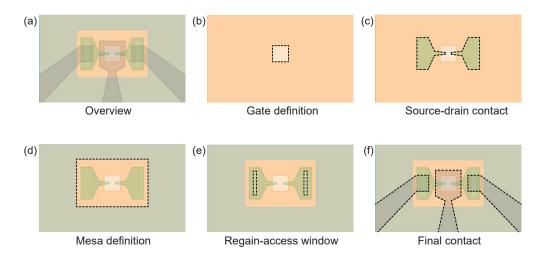

| A.1  | Lithography patterns for the improved compact design. (a) Overview of the device design. (b) Gate definition. The region outside the gate (the dashed box) is to be etched. (c) Source-drain contact. The finger-shaped contact is patterned for the metallisation. The overlap between the gate stack and the contact ensures a close contact to the gate after the lift-off process. (d) Mesa definition. The region outside the mesa (the dashed box) is to be etched. (e) Regain-access window. Two windows are opened on the source-drain contact by removing the alumina passivation. (f) Final contact. Final metallisation is done to bridge the source-drain contact to contact pads for subsequent |       |

# Chapter 1

## Introduction

#### 1.1 Motivation

Modern computers are based on von Neumann architecture where data are stored in memory, separately from and need to be fetched upon request by central processing unit (CPU). Memory is a fundamental requirement for computation. The \$167 billion per annum memory market is dominated by dynamic random-access memory (DRAM) and flash [1]. DRAM is capable of operating at high speed and is used as the main memory in computing. Conversely, the low cost and non-volatility of flash make it highly suitable as a storage memory. However, both DRAM and flash have significant drawbacks. DRAM's volatility, need of continuous refreshing and destructive-read process are inconvenient and inefficient. The penalty paid by flash for its non-volatility is high-voltage program and erase, making it intrinsically slow and damaging to its oxide barrier, leading to poor endurance. The trade-off between non-volatility and operation speed/energy efficiency of conventional memory hinders it from being capable of meeting the ever-increasing data abundancy in the information technology era.

For these reasons, the search for a memory technology that combines the speed of DRAM with the non-volatility of flash has continued unabated for decades, resulting in the development of so-called 'emerging memories' [2]. However, even though

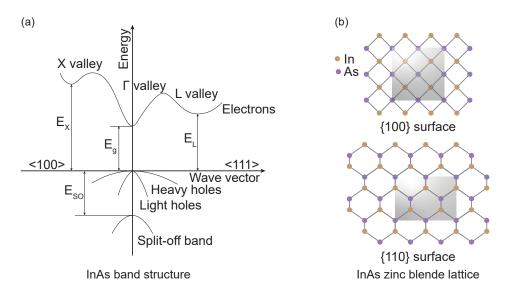

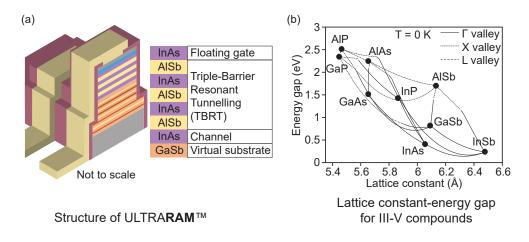

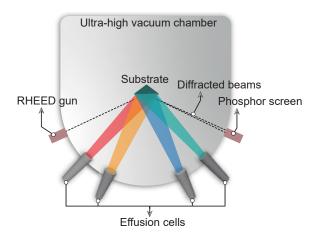

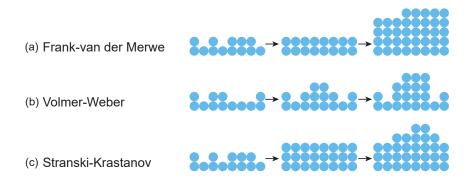

expected to reach \$36 billion in memory market by 2030 [3], emerging memories have not been able to match DRAM in terms of speed and switching energy. On the other hand, despite technical superiority to flash, no other memory can compete with its extremely low cost/bit. Furthermore, this has led to the widely-held perception that a compromise is required between low switching energy and non-volatility. In such a scenario, a so-called 'universal memory' with a robust state that is nevertheless easily changed is "not realistic" [4].