## Radial Tunnel Diodes based on InP/InGaAs Core-Shell Nanowires

Ofogh Tizno  $^{1,a)}$ , Bahram Ganjipour  $^{2,b)}$ , Magnus Heurlin  $^3$ , Claes Thelander  $^3$ , Magnus T. Borgström  $^3$  and Lars Samuelson  $^{3,c)}$

We report on the fabrication and characterization of radial tunnel diodes based on InP(n+)/InGaAs(p+) core-shell nanowires, where the effect of Zn-dopant precursor flow on the electrical properties of the devices is evaluated. Selective and local etching of the InGaAs shell is employed to access the nanowire core in the contact process. Devices with an  $n^+$ -p doping profile show normal diode rectification, whereas  $n^+$ - $p^+$  junctions exhibit typical tunnel diode characteristics with peak-to-valley current ratios up to 14 at room temperature and 100 at 4.2 K. A maximum peak current density of 28 A/cm² and reverse current density of 7.3 kA/cm² at  $V_{SD}$ =-0.5 V are extracted at room temperature after normalization with the effective junction area.

KEYWORDS: Heterostructure, Tunnel diode, Esaki diode, Nanowire, Core-shell, InP, InGaAs.

Tunnel diodes <sup>1</sup> are characterized by negative differential resistance (NDR) in the forward bias direction and zero bias reverse breakdown. Because of this particular current-voltage characteristic, combined with the very fast operation of tunnel diodes, they have been proposed for use in various RF microwave applications such as amplifiers and oscillators <sup>2-4</sup>

<sup>&</sup>lt;sup>1</sup>Physics Department, Lancaster University, Lancaster, LA1 4YB, United Kingdom

<sup>&</sup>lt;sup>2</sup>Department of Microtechnology and Nanoscience, Chalmers University of Technology, 412 96, Gothenburg, Sweden

<sup>&</sup>lt;sup>3</sup>Solid State Physics and NanoLund, Lund University, Box 118, SE-22100, Lund, Sweden

<sup>&</sup>lt;sup>a)</sup> This research was performed while Ofogh Tizno was at Solid State Physics and NanoLund, Lund University, Box 118, SE-22100, Lund, Sweden.

b) This research was performed while Bahram Ganjipour was at Solid State Physics and NanoLund, Lund University, Box 118, SE-22100, Lund, Sweden.

c) Author to whom correspondence should be addressed. Electronic mail: lars.samuelson@ftf.lth.se.

and are used in multi-junction solar cells <sup>5-7</sup>. In recent years, they have also attracted particular attention as building blocks for low power electronics. It is theoretically possible to obtain subthreshold swings steeper than the thermal limit of 60mV/decade at room temperature by fabricating transistors based on gated diodes with a p-i-n doping profile <sup>8-10</sup>. Recent developments in growth of epitaxial nanowires allow fabrication of nanowire electronic devices based on lattice mismatched semiconductor materials in axial and radial geometries <sup>11-14</sup>. Amongst these structures, nanowires based on radial heterojunctions are particularly attractive for field-effect transistor research due to the possibility of employing a wrap-gate <sup>15</sup>, and for cylindrical multi-junction solar cells <sup>16-19</sup> where they provide separate paths for light and charge collection <sup>20-22</sup>.

In this paper, we demonstrate the fabrication and electrical characterization of radial tunnel diodes based on InP(n+)/InGaAs(p+) core-shell nanowires. The effect of InGaAs shell doping concentration on the electrical properties of a series of fabricated devices is investigated. It is found that an NDR region appears under forward voltage bias for nanowires grown with higher Zn-dopant precursor flows. Esaki characteristics with peak-to-valley current ratios (PVCR) up to 14 are observed in the forward bias region at room temperature. Decreasing the temperature leads to a noticeable increase of the PVCR, with a highest value of 100 observed at liquid helium temperature.

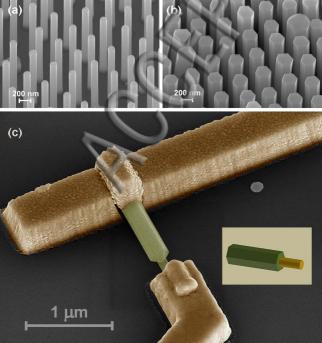

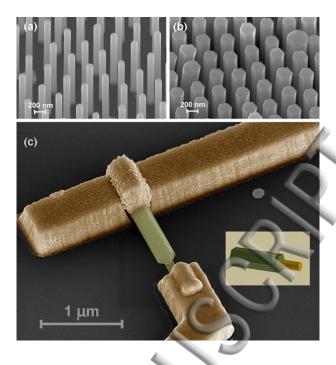

The nanowires were grown from nano-imprint lithography (NIL) defined Au particles inside holes of a 20 nm thick  $SiN_x$  mask deposited on (111) B InP substrates. The NIL pattern has a period of 400 nm with aligned columns of Au particles, where each column is slightly offset. The imprint process was carried out on 2" wafers with an Obducat AB developed process that uses an intermediate polymer stamp (IPS) and soft press technology  $^{23}$ . Before Au deposition the  $SiN_x$  was dry etched to expose the InP surface under the Au particle. The remaining  $SiN_x$  acted as a growth mask and prevented parasitic growth on the substrate

surface. The growth experiments were carried out in a horizontal flow, low pressure, metalorganic vapour phase epitaxy (MOVPE) reactor with a total flow of 6 l/min. The precursors used for growth were trimethylindium (TMIn), trimethylgallium (TMGa), arsine (AsH<sub>3</sub>), phosphine (PH<sub>3</sub>), hydrogen sulfide (H<sub>2</sub>S), and diethylzinc (DEZn). Hydrogen chloride (HCl) was used to impede radial growth while H<sub>2</sub> was used as the carrier gas <sup>24</sup>. The InP/InGaAs core-shell nanowire structure was fabricated in two steps <sup>25</sup>. Firstly, the InP core was grown at a temperature of 395 °C using molar fractions:  $\chi_{TMIn} = 8.2 \times 10^{-6}$ ,  $\chi_{PH3} = 18.5 \times 10^{-3}$ ,  $\chi_{H2S} = 6.7 \times 10^{-6}$  and  $\chi_{HCl} = 1.0 \times 10^{-5}$ . After the core growth, the nanowire samples were removed from the MOVPE reactor and the Au alloy particle was removed by wet etching using H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O (1:10) and KI:I<sub>2</sub>:H<sub>2</sub>O (4 g:1 g:40 mL) solutions at room temperature <sup>26</sup>. A second MOVPE step was used to grow an InGaAs shell on the InP nanowire cores at a growth temperature of 600 °C with  $\chi_{TMGa} = 1.9 \times 10^{-5}$ ,  $\chi_{TMIn} = 1.2 \times 10^{-5}$  and  $\chi_{AsH3} = 2.2 \times 10^{-3}$ . The amount of DEZn was varied in a series from  $\chi_{DEZn} = 0.16 \times 10^{-5}$  to  $4.6 \times 10^{-5}$ . Since the Au particle had been removed from the tip of the nanowires, axial growth was limited and most of the InGaAs material deposited on the nanowire sidewalls (Figure 1a and 1b).

After growth, the nanowires were broken off and transferred from the growth substrate to heavily *n*-doped silicon substrates capped with 100 nm thick SiO<sub>2</sub>. Single nanowire tunnel diodes were processed by fabricating drain and source metal contacts to the core and to the InGaAs shell of selected nanowires using electron beam lithography (EBL) and thermal evaporation.

Figure 1: (a) As grown InP nanowires after removing the Au particle. (b) InP/InGaAs Core-shell nanowires. (c) The fabricated InP/InGaAs radial tunnel diode with two electrical contacts on the core and the shell of the nanowire. The inset shows a schematic of the nanowire after selective etching of the InGaAs shell.

Contact to the nanowire core was achieved by selective etching of the InGaAs shell at one end of selected nanowires using EBL and wet chemical etching. Subsequent to an oxygen plasma ashing of the exposed area, wet chemical etching was used to remove the InGaAs shell from the entire contact area. The etchant solution offering the best observed selectively and etch depth was <sup>27</sup>: A=H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O (ratio of 1:1:8) and B=C<sub>6</sub>H<sub>8</sub>O<sub>7</sub>:H<sub>2</sub>O (ratio of 1:1). The two components A and B were prepared and mixed at room temperature immediately before use with the amount of solution B being equal to the amount of hydrogen peroxide in solution A. The wet etching creates a necessary undercut preventing an electrical short-circuit between the source and drain contacts. Metallization was done by thermal evaporation of Ti/Au (20/250 nm) to obtain the electrical contacts to the InP core. The InGaAs shell contact was defined in another EBL step followed by thermal evaporation of 20 nm Pd and 300 nm Au. Prior to shell contact metallization, the exposed nanowire contact areas were etched with

buffered HF for 15 s to remove the native oxide. Figure 1c shows an SEM micrograph of a fabricated device.

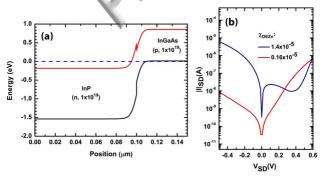

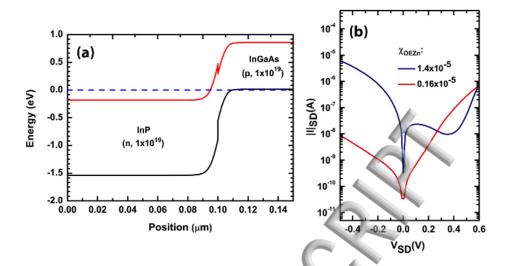

In order to investigate the room temperature band-to-band tunnelling (BTBT) mechanism in InP/InGaAs core-shell nanowires individual devices were electrically characterised in darkness and under vacuum conditions. A minimum of ten functioning devices were simultaneously fabricated from the corresponding wafer for each of the quoted flow rates. The data given herein corresponds to typical device parameters for each group. A liquid helium environment was used for the temperature dependent measurements. In all measurements the drain voltage,  $V_{SD}$ , was applied to the InGaAs shell while the n segment, InP core, was fixed at ground potential. In this set of experiments, three groups of nanowires with different Zn precursor flow during the shell growth were studied and a correlated distribution of electrical properties was observed from devices in the same doping groups. In order to elucidate the physical mechanism of the deduced I-V curves, a simulated band structure of an InP/InGaAs heterostructure is illustrated in Figure 2a. The band structure was calculated using Bandprof with an assumed doping concentration of  $10^{19}$  cm<sup>-3</sup> on either side of the junction  $^{28}$ .

Figure 2: (a) Room temperature equilibrium band structure of the InP(n++)/InGaAs(p++) tunnel diode, with assumed  $n=p=1\times10^{19}$  doping concentration on either side of the junction.(b) Output characteristics of two devices with  $\chi_{DEZn}$  of  $0.16\times10^{-5}$  and  $1.4\times10^{-5}$ . An obvious increase in tunnelling properties by increasing the applied  $\chi_{DEZn}$  can be seen.

Figure 2b shows room temperature I-V characteristics of two representative devices with different  $\chi_{DEZn}$  applied during the growth process. Nanowires fabricated from a sample grown with low  $\chi_{DEZn}$  (0.16×10<sup>-5</sup>), exhibit rectifying diode characteristics with rectification ratios of ~10<sup>2</sup> at ±0.5 V. An ideality factor of 2.26 is extracted for this device at biases where the diffusion current component dominates. This number is higher than that of an ideal p-n junction ( $\eta$ =1), which we attribute to the high n-doping in the InP core leading to carrier recombination across the depletion region via trap assisted states.

Increasing the DEZn flow during the growth results in nanowires that show typical tunnel diode behaviour with a clear NDR region under forward bias. The blue curve in Figure 2b shows the I-V characteristics of a nanowire grown with  $\chi_{DEZn} = 1.4 \times 10^{-5}$ . The nanowire device itemised here had maximum observed peak and reverse current densities of 28 A/cm<sup>2</sup> and  $7.3 \text{ kA/cm}^2$  (at  $V_{SD}$ =-0.5V) normalised to the effective tunnelling junction area as estimated from SEM measurements. Although the BTBT can clearly be attributed to the

increased doping of the InGaAs shell, further studies are needed to determine the precise doping concentration of the materials.

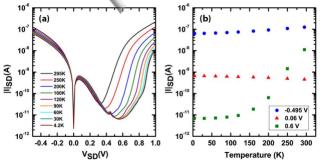

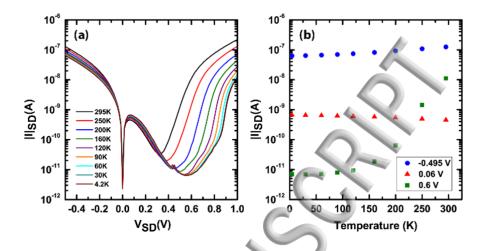

Figure 3: (a) Current-voltage characteristic of an InP/InGaAs tunnel diode at different temperatures ranging from 4.2 K to 295 K. (b) Absolute current versus temperature at selected biases of -0.495 V, 0.06 V and 0.6 V.

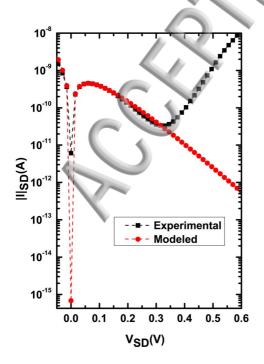

Nanowires grown with even higher Zn precursor flow,  $\chi_{DEZn}$  of  $4.6 \times 10^{-5}$ , showed improved PVCRs, however at the expense of lower diode and BTBT currents. Figure 3a and 3b show the detailed temperature dependent output characteristics of a device with the highest observed PVCR ( $\chi_{DEZn} = 4.6 \times 10^{-5}$ ). As shown by the black curve in the Figure 3a, at room temperature a peak current density of 0.39 A/cm<sup>2</sup> is measured at a voltage of Vp=0.06 V. At slightly higher voltages, direct band-to-band tunnelling current vanishes, resulting in an observed valley current density of 0.029 A/cm<sup>2</sup> and a PVCR of 14. Moreover, the current in this region fits well to the theoretical model for direct band-to-band tunnelling which dominates at low biases (Figure 4):

$$I_{BTBT} = I_P \left(\frac{V}{V_P}\right) exp\left(1 - \frac{V}{V_P}\right) \tag{1}$$

where  $I_{BTBT}$  is the band-to-band tunnelling current,  $V_{SD}$  is the voltage across the heterojunction and  $I_P$  and  $V_P$  are the peak current and peak voltage, respectively.

Figure 4: Room temperature band-to-band tunnelling at small biases. Black squares illustrate the absolute current versus bias for an InP/InGaAs radial tunnel diode with  $4.6 \times 10^{-5} \chi_{DEZn}$  during the shell growth. Red circles represent the data predicted by modelling.

Unlike conventional diodes, in which the current flow is blocked up to the point known as the reverse breakdown voltage, the onset voltage of the reverse breakdown in a tunnel junction becomes zero due to the high dopant concentrations on either side of the junction. As shown in the Figure 3, under reverse bias conditions the increased overlap between valence band states in the *p*-region and available conduction band states in the *n*-region leads to a significant tunnelling current flow through the junction. The small decrease in reverse current with temperature shown in Figures 3a and 3b is due to an increase in series resistances at increasingly negative voltage values as well as the small change in the band gap. The peak current in the forward direction increases with reducing temperature despite an increased band gap (Figure 3b). This can be attributed to the decreased thermal spread of the Fermi function at low temperatures, implying that more energy states can contribute to the tunnelling process <sup>29</sup>. In contrast to the peak current, the peak voltage value is insensitive to

temperature as it is defined by the position of the Fermi levels on both sides far from the junction <sup>30</sup>.

Increasing the bias beyond the tunnelling current peak results in a decrease in interband tunnelling due to the decreased overlap between electron and hole states in the *n* and *p* regions, manifesting in the observed NDR region in the forward bias characteristic. The direct BTBT current thus drops and eventually falls to a minimum known as the valley current where tunnelling via midgap defect states dominates. It is worth noting that in a degenerately-doped tunnel junction often only a small fraction of the valley current is due to the conventional *p-n* junction current. Instead, the dominating current is typically the so-called *excess* current, generally caused by indirect electron tunnelling via energy states located in the forbidden energy gap. These local energy levels are introduced by crystal defects, dislocations or donor and acceptor impurities during the junction fabrication. It is well known that degenerately-doped semiconductors are associated with exponential extensions of both conduction and valence band-edge tails into the forbidden energy gap, producing a range of available energy levels for tunnelling <sup>31</sup>. Figure 3a indicates that the excess current is strongly temperature dependent, which is the expected behaviour for tunnelling via prid-gap trap states.

The green curve in Figure 3b shows the variation of the excess current with temperature at a source-drain bias of 0.6 V. The excess current decreases rapidly with falling temperature, and as a result, the PVCR increases from 14 at room temperature to 100 at liquid helium temperature. These high PVCR's represent very low excess current at the junction resulting from epitaxial growth of a small cross-section, low defect interface in this sample.

TABLE I: Currents and PVCR for the InP(n+)/InGaAs(p+) radial tunnel diode at room temperature.

| DEZn                  | 295K     |                              |                   |                   |      |

|-----------------------|----------|------------------------------|-------------------|-------------------|------|

| Molar                 |          | J <sub>R</sub>   (V= -0.5 V) | $J_{p}$           | $J_{v}$           | PVCR |

| fraction              |          | A/cm <sup>2</sup>            | A/cm <sup>2</sup> | A/cm <sup>2</sup> | TVCK |

| 0.16×10 <sup>-5</sup> | Device A | 7.7                          |                   |                   |      |

|                       | Device B | 20                           |                   |                   |      |

|                       | Device C | 43                           |                   |                   | 4    |

| 1.4×10 <sup>-5</sup>  | Device A | 7300                         | 28.6              | 11.3              | 2.5  |

|                       | Device B | 5600                         | 9                 | 2                 | 4.5  |

|                       | Device C | 6400                         | 12.5              | 8                 | 1.5  |

| 4.6×10 <sup>-5</sup>  | Device A | 112                          | 0.39              | 0.0286            | 14   |

|                       | Device B | 330                          | 0.5               | 0.06              | 8    |

|                       | Device C | 343                          | 2                 | 0.2               | 10   |

At sufficiently high voltages (>0.4 V), the current is dominated by thermal diffusion of electrons from the conduction band on the InP side to the conduction band on the InGaAs side across the barrier formed at the heterointerface. This current component is also strongly temperature dependent as shown in Figure 3a. Table I provides a summary of the extracted properties for the devices discussed here together with other example nanowire devices from each different DEZn molar fraction group.

What is immediately clear in table I is the influence of higher Zn doping on devices characteristics. The nanowires grown with the high  $\chi_{DEZn}$  of  $4.6\times10^{-5}$  show lower current density with higher PVCR compared to those grown with the  $\chi_{DEZn}$  of  $1.4\times10^{-5}$ . This may be explained by the fact that incorporation of Zn into the InGaAs crystal lattice first increases with increasing precursor molar fraction and then at some point decreases, resulting in lower hole concentration and consequently, lower tunnelling currents  $^{32}$ .

Further, a large diffusion coefficient has been reported for Zn in the presence of a heavily doped n-type material <sup>33</sup>. Specifically, the increase in the free electron concentration and Fermi level in the crystal increases the thermal equilibrium concentration of negatively charged group III vacancies <sup>34</sup>. Zn diffusion into the n-type InP layer therefore alters the interface between the two materials, widening the depletion region and consequently increasing the potential barrier and the reducing tunnelling probability.

In conclusion, we have demonstrated radial tunnel diodes based on InP/InGaAs coreshell nanowires. With increasing  $\chi_{DEZn}$  flows during the InGaAs shell growth a transition in junction properties was observed, from rectifying p-n junctions to tunnel diodes. Nanowire junctions grown with even higher  $\chi_{DEZn}$  flows showed PVCR up to 14 at room temperature, and 100 at liquid helium temperature, at the expense of reduced current levels. A relatively high PVCR in this material system indicates the possibility of a low defect state density close to the heterointerface, which makes this material system attractive for various electronic and photonic applications. Furthermore, it proposes use for the study of the physics of the radial tunnel diode structures and the epitaxial growth processes necessary to realise high quality heterojunctions.

This work was performed within the NanoLund centre at Lund University, supported by the Swedish Research Council (VR), the Foundation for Strategic Research (SSF), the Knut and Alice Wallenberg Foundation (KAW) and the Swedish Energy Agency (SEA).

## **References:**

- <sup>1</sup>L. Esaki, Phys. Rev., **109**, 603 (1958).

- <sup>2</sup>H. C. Okean, IEEE Transactions on Microwave Theory and Techniques, **15**, 613 (1967).

- <sup>3</sup>C. T. Van Degrift, Rev. Sci. Instrum, **46**, 599 (1975).

- <sup>4</sup>N. Muramatsu, H. Okazaki, T. Waho, in *Circuits and Systems, 2005: proceedings of the IEEE International Symposium on Circuits and Systems, ISCAS*, Kobe, Japan, 23-26 May 2005, pp. 2341-2344.

- <sup>5</sup>J. Fariborz, S. Mirzakuchaki, International Journal of Modern Engineering Research, **2**, 4014 (2012).

- <sup>6</sup>A. W. Bett, R. Adelhelm, C. Agert, R. Beckert, F. Dimroth and U. Schubert, Solar Energy Mater. Solar Cells., **66**, 541 (2001).

- <sup>7</sup>M. Yamaguchi, T. Takamoto and K. Araki, Solar Energy Mater. Solar Cells., **90**, 3068 (2006).

- <sup>8</sup>R. Gandhi, Z. Chen, N. Singh, K. Banerjee and S. Lee, IEEE Electron Device Lett., 32, 437 (2011).

- <sup>9</sup>B. Ganjipour, J. Wallentin, M. T. Borgström, L. Samuelson and C. Thelander, ACS Nano, **6**, 3109 (2012).

- <sup>10</sup>H. Lu and A. Seabaugh, IEEE J. Electron Devices Soc., **2**, 44 (2014).

- <sup>11</sup>R. He and P. Yang, Nature Nanotechnology, 1, 42 (2006).

- <sup>12</sup>X. L. Feng, R. He, P. Yang, and M. L. Roukes, Nano Lett., 7, 1953 (2007).

- <sup>13</sup>C. K. Chan, H. Peng, G. Liu, K. McIlwrath, X. F. Zhang, R. A. Huggins and Y. Cui, Nature Nanotechnology, **3**, 31 (2008).

- <sup>14</sup>J. Wallentin, N. Anttu, D. Asoli, M. Huffman, I. Åberg, M. H. Magnusson, G. Siefer, P. Fuss-Kailuweit, F. Dimroth, B. Witzigmann, H. Q. Xu, L. Samuelson, K. Deppert, M. T. Borgström, Science, 339, 1057 (2013).

- <sup>15</sup>A. W. Dey, J. Svensson, M. Ek, E. Lind, C. Thelander and L. E. Wernersson, Nano Lett., **13**, 5919 (2013).

- <sup>16</sup>B. Tian, X. Zheng, T. J. Kempa, Y. Fang, N. Yu, G. Yu, J. Huang and C. M. Lieber, Nature, 449, 885 (2007).

- <sup>17</sup>M. Yoshimura, E. Nakai, K. Tomioka, and T. Fukui, Appl. Phys. Exp., 6, 052301 (2013).

- <sup>18</sup>G. Mariani, A. C. Scofield, C. H. Hung and D. L. Huffaker, Nature Communications, **4**, 1497 (2013).

- <sup>19</sup>P. Krogstrup, H. I. Jørgensen, M. Heiss, O. Demichel, J. V. Holm, M. Aagesen, J. Nygard and A. Fontcuberta i Morral, Nature Photonics, 7, 306 (2013).

- <sup>20</sup>S. L. Diedenhofen, O. T. A. Janssen, G. Grzela, E. P. A. M. Bakkers and J. Gómez Rivas, ACS Nano, 5, 2316 (2011).

- <sup>21</sup>B. M. Kayes, H. A. Atwater and N. S. Lewis, J. Appl. Phys., **97**, 114302 (2005).

- <sup>22</sup>K. R. Catchpole, S. Mokkapati, and F. J. Beck, J. Appl. Phys., **109**, 084519 (2011).

- <sup>23</sup>T. Eriksson, S. Yamada, P. V. Krishnan, S. Ramasamy, B. Heidari, Microelectronic Engineering, **88**, 293 (2011).

- <sup>24</sup>M. T. Borgström, J. Wallentin, J. Trägårdh, P. Ramvall, M. Ek, L. R. Wallenberg L. Samuelson and K. Deppert, Nano Res., **3**, 264 (2010)

<sup>25</sup>M. Heurlin, T. Stankevič, S. Mickevičius, S. Yngman, D. Lindgren, A. Mikkelsen, R. Feidenhans'l, M. T. Borgström, and L. Samuelson, Nano Lett., 15, 2462 (2015).

<sup>26</sup>M. Heurlin, O. Hultin, K. Storm, D. Lindgren, M. T. Borgström and L. Samuelson, Nano Lett., **14**, 749 (2014).

<sup>27</sup>M. Górska, H. Wrzesińska, A. Szerling, K. Hejduk, J. Ratajczak, J. M. Łysko, Mat. Sci.-Poland, **23**, 221 (2005).

<sup>28</sup>W.R. Frensley, IEEE Transactions on Electron Devices, **38**, 2704 (1991).

<sup>29</sup>J. R. Söderström, D. H. Chow and T. C. McGill, Appl. Phys. Lett., **55**, 1094 (1989).

<sup>30</sup>D. Meyerhofer, G. A. Brown and H. S. Sommers, Phys. Rev., **126**, 1329 (1962).

<sup>31</sup>P. Van Mieghem, Rev. Mod. Phys., **64**, 755 (1992).

<sup>32</sup>T. Lin, L. Jiang, X. Wei, G. H. Wang, G. Z. Zhang, X. Y. Ma, J. Cryst. Growth, **261**, 490 (2004).

<sup>33</sup>K. Kurishima, T. Kobayashi, and U. Gösele, Appl. Phys. Lett. **60**, 2496 (1992).

<sup>34</sup>K. Kurishima, T. Kobayashi, H. Ito, and U. Gösele, J. Appl. Phys. **79**, 4017 (1996).