**ACCESS** I

ACS APPLIED

Article

# Charge Transport Regimes of MoS<sub>2</sub> Nanosheets at Cryogenic **Temperatures: Implications for Cryogenic Electronics**

Michael D. Thompson,\* Matthew Haworth, Owain T. Hughes, Jonathan Prance, Yuri Pashkin, Luca Panarella, Farzan Gity, Gioele Mirabelli, Giorgos Fagas, and Ray Duffy\*

NANO MATERIALS

ABSTRACT: The electron transport of n-type back-gated MoS<sub>2</sub> field-effect transistors is investigated in the temperature range of 0.3-271 K. The electrical characteristics exhibit significant variations in the drain current in the subthreshold region, when the drain voltage is sufficiently low. The data analysis reveals two distinct charge transport mechanisms at high temperatures. At high gate voltages, charge transport is well described by variable range hopping theory, which suggests the Efros-Shklovskii regime, while at low gate voltages, we observe a transition to the conventional thermal activation regime. The observed phenomena are at considerably greater device dimensions compared to previously reported, as going to sub-Kelvin regimes loosens the dimensional restraints on the device. Moreover, a huge temperature-dependent threshold voltage shift  $(\delta V_{\rm TH}/\delta T)$  is observed in the whole temperature range, approximately 110 mV/K, incredibly spanning as much as 30 V, with  $V_{\mathrm{TH}}$  increasingly more positive with decreasing temperature. Evidence of a resistive network for charge carriers is also seen, as there appeared to be parallel channels of conduction within the FETs, each with a different threshold voltage. All this physics needs to be factored in should 2D material FETs be considered for quantum electronics at cryogenic temperatures.

**KEYWORDS:** field-effect transistor, MoS<sub>2</sub>, charge transport, variable range hopping, thermal activation

## 1. INTRODUCTION

Quantum nanoelectronics is concerned with charge transport in nanoscale devices functional in the quantum regime. Electronic studies at sub-Kelvin temperatures are necessary to understand both a material's suitability in quantum devices and the physics of the device characteristics. For example, group IV and III-V nanostructured devices have been typically characterized by electron transport measurements biased across cryogenic temperatures (mK-K) and at low-to-high frequencies (DC-GHz) to be used for charge- or spin-based qubit formation, manipulation, and operation. In this work, we report on functional MoS<sub>2</sub> field-effect transistor (FET) devices down to the sub-K regime and analyze their transport characteristics in order to understand the capabilities of, and physics in, transition metal dichalcogenides (TMDs) applied to quantum nanoelectronics.

Two-dimensional (2D) TMD materials not only present themselves as promising candidates for advanced transistor scaling and ultrahigh integration of solid-state electronic switching devices but also offer a wide range of material properties and the possibility of forming artificial quantum objects, such as single-photon emitters, quantum dots, and topological states, paving the way for their application in quantum information science.1 For analog devices, 2D semiconductors are also particularly suitable for building substrate-agnostic integrated circuits, such as operational

October 22, 2025 Received: Revised: November 20, 2025 Accepted: November 21, 2025

**ACS Applied Nano Materials**

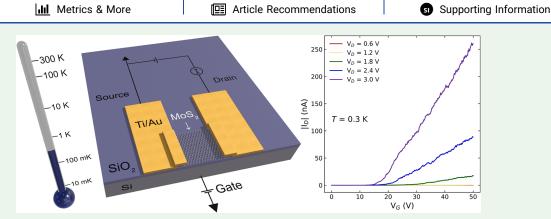

Figure 1. (a) Schematic of the device fabrication. A few nm thick flake of exfoliated  $MoS_2$  is placed onto a  $SiO_2/Si$  substrate followed by deposition of Ti/Au contacts. (b) and (c) Representative transfer characteristics of an n-type  $MoS_2$ -based MOSFET at 0.3 K, with varying drain potential and (d) at low  $V_D$  (0.6 V), with temperature varying from 0.3 to 20 K. (e) Current–voltage characteristics for  $V_G = 50$  V at varying temperatures.

amplifiers,<sup>2</sup> which could, for example, be directly integrated with superconducting quantum circuits at cryogenic temperatures.

Should functional TMD FETs be fabricated for quantum or space applications, one must be aware of new physical phenomena or peculiarities that become evident once thermal noise is reduced. To date, the few studies dealing with TMD-based FETs at cryogenic temperatures reported working devices at temperatures no lower than a few Kelvin degrees. These studies are also mainly focused on evaluating performance<sup>3</sup> or obtaining low-resistance ohmic contacts,<sup>4</sup> rather than investigating the underlying physics of 2D materials' FET electronic behavior at very low temperatures. Here, we demonstrate sub-K operation of n-type back-gated MoS<sub>2</sub> FETs and study their electrical characteristics in these operating regimes, up to room temperature, aiming at characterizing the new features in the charge transport of the MoS<sub>2</sub> material.

Overall, apart from a few select works, such as that by Hamilton,<sup>5</sup> with differential conductance maps at <10 mK, the electrical properties of 2D TMDs have not been adequately examined at the sub-K threshold. Kim et al. investigated how the electrical properties of Ohmic van der Waals contacts of MoS<sub>2</sub>/In interfaces such as conductance, carrier mobility, and contact resistance vary with temperature in cryogenic regimes.<sup>6</sup> They observed Ohmic-like transport based on a field-emission mechanism in the contacts from 2.4 to 300 K, in addition to a small interfacial charge. Similarly, Gao et al.<sup>7</sup> examined the

transfer characteristics, transconductance, and radio frequency performance of chemical vapor deposition-grown MoS<sub>2</sub> films, demonstrating maximum extrinsic and intrinsic cutoff frequencies of 16 and 24 GHz as well as a maximum transconductance of 35  $\mu$ S/ $\mu$ m at 4.3 K. Optimal electrical performance of alloy contacts with other 2D TMDs at comparable temperatures was demonstrated in WS<sub>2</sub>, examining carrier mobility versus temperature, at different drain voltages, as well as contact resistance versus temperature, down to 3 K. Notably, the devices exhibited low contact resistances of  $\approx 10$  $k\Omega \cdot \mu m$  at 3 K and Schottky barrier heights of 1.7 meV. The electrical characteristics of other electronic devices such as memtransistors, which have potential applications in neuromorphic computing, have also been extensively studied by Sangwan et al. Subtleties, such as hysteresis differences in the transfer characteristics, between FETs and memtransistors should be considered when comparing these different devices.

## 2. EXPERIMENTAL METHODS

**2.1. Sample Fabrication.** In this work,  $MoS_2$  devices were fabricated in the standard way using exfoliated flakes from a single crystal;  $^{10-12}$  further information can be found in the Supporting Information and Figure S1. In short, devices were fabricated by mechanical exfoliation from  $MoS_2$  single crystals, followed by the transfer of the resulting layers onto  $Si/SiO_2$  substrates, and completed with Ti/Au metal contact pad formation as shown in Figure 1a.

**2.2. Electrical Characterization.** Prior to cryogenic testing, devices were initially checked at room temperature to verify basic FET operation, such as current conduction and gate-bias current

modulation over several orders of magnitude. Cryogenic measurements were taken in an Oxford Instruments Triton 400 dilution refrigerator (<1 K) and an Oxford Instruments IO 1 K refrigerator (1–300 K) with a 2-terminal configuration using a Keithley 2400 source-measure unit (SMU) and a second SMU for applying a backgate voltage.

## 3. RESULTS AND DISCUSSION

Figure 1b,c shows representative transfer characteristics of a MoS<sub>2</sub>-based FET at 0.3 K. It is greatly encouraging to observe functional transistor operation of MoS<sub>2</sub> devices at sub-Kelvin temperatures, making this family of devices viable to integrate in quantum electronic circuits that operate at these temperatures. For clarity, the same data are plotted with linear and log y-axis scales in Figure 1b,c. The device is turned on at positive gate potentials  $(V_G)$ , with a drain current  $(I_D)$  that increases with increasing positive gate voltage, suggesting an n-type behavior. The drain current does not saturate within the investigated potential range, as seen in the current-voltage (IV) characteristics in Figure 1e which also shows the diodelike effect of the IV curves at low temperature. Further IV characteristics are shown in Figures S4 and S5 where we observe the IV to be linear at room temperature with only a weak tendency toward saturation observed at low gate voltage. A clear shift of the threshold voltage  $(V_{TH})$  is observed caused by varying the drain potential  $(V_D)$ , possibly due to draininduced barrier lowering. Note the significant current variations of the  $I_{\rm D}$  versus  $V_{\rm G}$  characteristics present in the different curves visible in Figure 1b,c. Such variations cannot be ascribed to instrumental noise due to very low signals, as they are significantly above the sensitivity limit of the measurement setup. Notably, Lee et al. observed current variations in monolayer  $MoS_2$  at 6 K with  $V_D$  = 100  $\mu V$ , ascribed to the Coulomb blockade effect. 13 Equivalent behavior was seen in a p-type MoS<sub>2</sub>-based FET, shown in Figure S2, where that device was fabricated from a flake exfoliated from an intentionally Nb-doped MoS<sub>2</sub> crystal, and the flake in question was 9 nm thick. In the remainder of this article, we will focus on the n-type MoS2-based FETs for consistency.

The above-mentioned variations are more clearly presented in Figure 1d. Note that the same data are plotted with a log-scale y-axis in Figure S3. Here, the transfer characteristics at  $T=0.3-20~\rm K$ ,  $V_{\rm D}=0.6~\rm V$ , and  $V_{\rm G}=0-50~\rm V$  are shown. This unusual characteristic was reproducible across many low temperatures and appeared in both n- and p-type FETs, particularly noticeable at low  $V_{\rm D}$  and in the subthreshold region. In most circumstances, when studying large-dimension metal-oxide-semiconductor field-effect-transistor (MOSFET) device behavior, say Si MOSFETs at room temperature, one would not expect to see such variations in current.

For comparison, Si MOSFETs have been studied at cryogenic temperatures, <sup>14–22</sup> with many works focusing on the subthreshold slope during turn-on. In some cases, smallarea Si MOSFETs exhibit variations in subthreshold current at deep cryogenic temperatures. Such variations have been ascribed to the density of states band-tails, or carriers undergoing resonant tunneling through the channel, or percolation theory, due to electrostatic potential fluctuations caused by interface charges. <sup>23,24</sup> Finally, very recently Cherkaoui et al. studied high-k dielectric/InGaAs interface defects at cryogenic temperatures<sup>25</sup> and showed that the exchange of free carriers between oxide states and the

conduction or the valence band is strongly temperature-dependent.

At higher temperatures (>30 K), variable range hopping (VRH) has been identified as the transport mechanism in previous reports on WS<sub>2</sub><sup>8</sup> and MoS<sub>2</sub>.<sup>26–29</sup> This form of transport manifests itself as a temperature-dependent resistivity of the following form:

$$\rho = \rho_0 \exp(T_0 T)^p \tag{1}$$

where  $\rho_0 = AT^m$  (m is an empirical prefactor exponent),  $T_0$  is a characteristic temperature, and p = 1/(d+1), where d is the effective dimensionality of the system. WRH hopping occurs in compensated semiconductors at temperatures where impurities are frozen out and electrons hop between impurities rather than entering the conduction band.

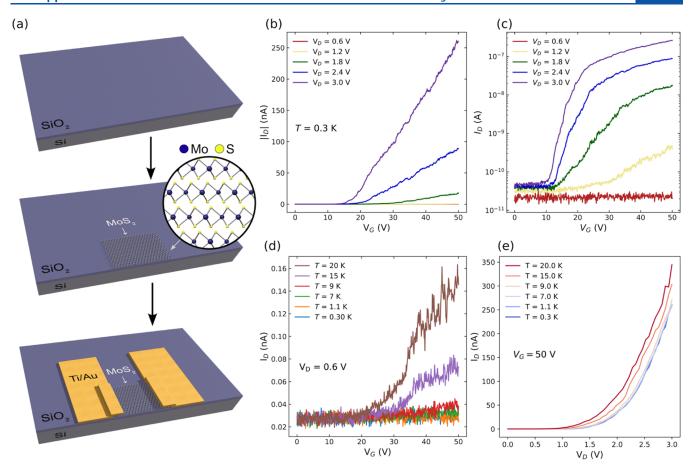

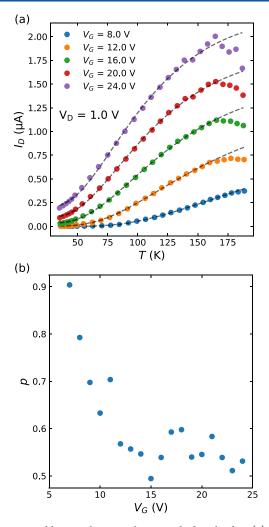

One signature of VRH transport is a linear dependence of  $\ln(\rho/T^m)$  against  $T^{-p}$  as reported previously;  $^{32,33}$  however, if  $T_0$  is small, then at high temperature, the exponential in eq 1 becomes sufficiently small that this dependence can be fit linearly for any realistic value of p. In order to identify whether such transport is evident in our samples, we apply eq 1 to the current versus temperature data, using m=1, in order to extract p for different gate voltages, as seen in Figure 2a, noting that  $\rho \propto 1/I_{\rm D}$  as the device is in the linear region. From this, we can determine p as a function of  $V_{\rm G}$  seen in Figure 2b. Here, we find that p tends to saturate at a value close to 1/2 at higher gate voltages. While this would suggest that the dimensionality of the electron system is 1, it is more likely a signature of Efros—Shklovskii hopping  $^{33}$  where the Coulomb interaction opens up a gap in the density of states.

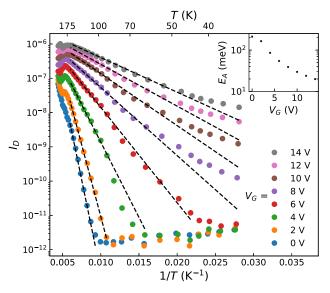

At lower gate voltages, VRH hopping does not appear to be the dominant transport mechanism. Figure 3 shows an Arrhenius plot of  $I_{\rm D}$  for low gate voltages indicating that charge transport appears to be thermally activated for  $V_{\rm G} < 8$  V,

$$I = I_0 e^{-E_A/k_B T} \tag{2}$$

where  $I_0$  is a prefactor,  $k_{\rm B}$  is the Boltzmann constant, and  $E_{\rm A}$  is the activation energy and is shown as a function of gate voltage in the inset of Figure 3. At  $V_{\rm G} > 8$  V, the temperature dependence cannot be explained by thermal activation, presumably due to the transition to the VRH regime. Thermionic emission was also considered, however there was no evidence of this in the data. Above 175 K, we observed a change in the device characteristics for which we currently do not have an explanation and requires future study.

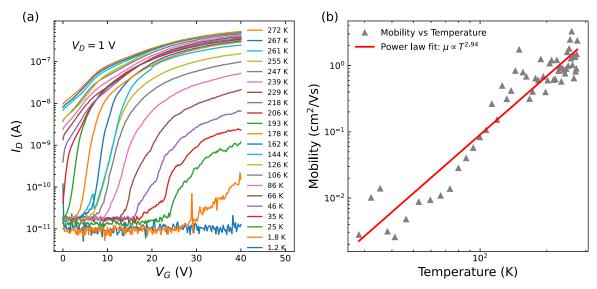

Figure 4a shows representative  $I_D$  versus  $V_G$  characteristics with  $V_D$  = 1 V across a very wide range of temperatures, increasing from 1.2 to 272 K. N-type transfer behavior is observed as before. However,  $V_{\mathrm{TH}}$  and the on-state current  $(I_{\text{D-ON}})$  change drastically. Estimating  $V_{\text{TH}}$  by a simple threshold of 1 nA, we find that with lower temperatures,  $V_{\mathrm{TH}}$ increases by approximately 30 V, which could have a significant impact of design for MoS2-based circuits, where typically one does not want large shifts in performance as temperature changes.  $I_{D-ON}$  decreases by about 4 orders of magnitude, while still appearing to plateau for  $V_{\rm G}\gg V_{\rm TH}$ . This positive shift in  $V_{

m TH}$  with lower temperature indicates that it is more difficult to invert a channel or to accumulate charge carriers, while the reduced  $I_{\text{D-ON}}$  indicates that the channel is more resistive. The trend of increased device resistance with decreasing temperature is consistent with our previous works on 2D material **ACS Applied Nano Materials**

**Figure 2.** Variable range hopping theory applied to the data (a) fitting eq 1 (dashed lines) for a selection of gate voltages with  $V_{\rm D}=1.0~{\rm V}$ . The fitting starts to deviate above 160 K. The extracted values for p across a wider range of gate voltages are shown in (b). Here, we see that p tends to saturate slightly above 1/2. See Figures S4 and S5 for additional information about the linear regime of the device at these biases and temperatures.

devices. <sup>34,35</sup> Of course, carrier mobility can drop due to increased impurity scattering at lower temperatures, but a 4 orders of magnitude drop in  $I_{\text{D-ON}}$  would require an equivalent drop in mobility, as established MOS theory suggests  $I_{\text{D-ON}}$  and mobility have a linear relationship. There is evidence of  $\delta V_{\text{TH}}/\delta T$  in the work of Ghatak et al., in 3- and 1-layer MoS<sub>2</sub>, with their data presented and discussed in terms of conductivity. <sup>32</sup>

A >100 mV/K temperature-dependent  $V_{\rm TH}$  is worth contrasting with values found in Si devices, and it is important to consider the underlying cause. In early works, Tzou et al. <sup>36</sup> and Klaassen et al. <sup>37</sup> observed a positive  $V_{\rm TH}$  shift  $(\delta V_{\rm TH}/\delta T)$  in n-type FETs with decreasing temperature, as we do, however, with a range of 1–2 mV/K, vastly lower than what we observe in MoS<sub>2</sub>. Furthermore, d'Alessandro et al. <sup>38</sup> did a survey of different models for  $\delta V_{\rm TH}/\delta T$ , while Nishida et al. <sup>39</sup> provided a very thought-provoking discussion and analysis on the potential sources of  $\delta V_{\rm TH}/\delta T$  in terms of the equation:

**Figure 3.** Arrhenius plot of  $I_{\rm D}$  for different back gate voltages with  $V_{\rm D}$  = 1.0 V. The dashed lines are linear fits to temperatures 80 K < T < 165 K according to eq 2. Fits have been extended beyond the fitting region to emphasize the nonlinearity at lower temperatures. The inset shows the activation energy  $E_{\rm A}$  as a function of gate voltage.

$$V_{\rm TH} = V_{\rm FB} + 2\phi_{\rm f} + \frac{\sqrt{4q\varepsilon_0\varepsilon_{\rm Si}N_{\rm a}\phi_{\rm f}}}{C_{\rm ox}} + \frac{eD_{\rm it}}{C_{\rm ox}}$$

(3)

where  $V_{\rm FB}$  is flat band voltage, the voltage where no band bending occurs,  $\phi_{\rm f}$  is the difference between the Fermi level  $(E_{\rm F})$  and the intrinsic level  $(E_{\rm i})$ , e is the electron charge,  $\varepsilon_0$  and  $\varepsilon_{\rm Si}$  are the vacuum and Si relative dielectric constants,  $N_{\rm a}$  is the doping concentration level,  $D_{\rm it}$  is the interface state density, and  $C_{\rm ox}$  is the gate capacitance. Note, this equation is included here to aid the discussion, rather than for fitting or parameter extraction purposes. Thus,  $\delta V_{\rm TH}/\delta T$  is subject to several potential causes, as many of the parameters in eq 3 are temperature-sensitive or contain factors that are temperature-dependent, and this should be studied in more depth in follow-up works to identify the key sources of  $\delta V_{\rm TH}/\delta T$  and reduce this effect in MoS<sub>2</sub> devices.

Figure 4b shows the mobility as a function of temperature, extracted using the H-function method by Chien et al. <sup>40</sup> An increasing mobility with temperature is typical when impurity scattering dominates <sup>41</sup> and a fit to the data shows a T<sup>3</sup> dependence though T<sup>3/2</sup> is expected. A high level of impurities is consistent with the sample's doping level and previous reports of high levels of impurities for exfoliated flakes. <sup>42</sup> The subthreshold swing is observed to have a stronger temperature dependence down to 150 K (Figure S6) and then saturates below this. A similar behavior is seen in Si MOSFETs <sup>18</sup> where the saturation is due to the presence of a band-tail. From the mobility temperature dependence, this would suggest that such a band-tail in our samples is due to a high level of impurities.

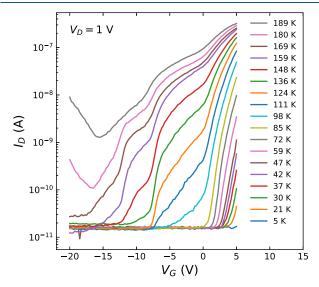

Figure 5 once again shows FET transfer behavior but is now concentrated on the subthreshold region at more negative  $V_{\rm G}$ . It can be observed in some cases that the device turns on in steps or stages, with alternatingly steep or shallow subthreshold slopes. In other words, the current turn-on appears to occur in a number of parallel channels that become active at different  $V_{\rm G}$ . Take for example, the T=159 K curve, there are turn-on events at  $V_{\rm G}=-12$ , -8, and +1 V, which could be considered as three separate threshold voltages for this device. Many

**ACS Applied Nano Materials**

Figure 4. (a) Representative transfer characteristics of an  $MoS_2$ -based MOSFET at 1.2–271.5 K with  $V_D = 1$  V. An approximate 110 mV/K temperature-dependent VTH is observed spanning approximately 30 V, increasingly more positive with decreasing temperature. (b) Mobility as a function of temperature for the data in (a).

Figure 5. Representative transfer characteristics of an  $MoS_2$ -based MOSFET at 3.7–190.5 K with  $V_{\rm D}=1$  V. These data show a resistor network-type conduction, namely a network of parallel transistors with different aspect ratios, and threshold voltages,  $V_{\rm TH}$ , leading to an unusual subthreshold slope variation. Note also, in comparison with Figure 4, we have measured a number of devices in this work, and when working with exfoliated flakes, there is some unavoidable device-to-device variability; however, the overall trends are the same. This will be solved in future work, namely, when we switch the study to  $MoS_2$  thin films.

curves in Figure 5, taken at different temperatures, show this type of behavior, which is unusual in FET devices that would normally have a single turn-on or channel formation event. Recently, for fully depleted SOI devices, Catapano et al. proposed a model based on the concept of resistive networks, linked to percolation transport theory. When the FET is on, in the presence of an inversion channel, transport can occur in randomly distributed low-resistive regions. Crucially, that group modeled the inversion layer as a network of parallel transistors with different aspect ratios (channel width/channel length) K and different  $V_{\rm TH}$ . With a variety of parallel channels

of different K and  $V_{\mathrm{TH}}$ , the result is a subthreshold slope with a mixture of "turn-on" points. It should be noted that in the reported works on Si FETs, this arbitrarily distributed low-resistive region effect was only observed in small-dimension (submicron) devices and not observed in micron-scale channels. In this work, not only do we see this in a non-Si device, but we observe this physics at significantly larger device dimensions, thereby relaxing the dimensional restraints on the fabrication processes and device design required to study this distinctive physics. We speculate that this behavior could be due to top or bottom edge conduction or side edge conduction, as grain boundaries are unlikely for exfoliated flakes.

#### 4. CONCLUSIONS

In conclusion, if TMD FETs are proposed for quantum or space applications, one must be aware of new physical phenomena or peculiarities that become evident once thermal noise is reduced. Based on cryogenic measurements taken in an Oxford Instruments Triton 400 dilution refrigerator down to sub-Kelvin temperatures, MoS2 FET devices exhibit a number of distinctive characteristics. Features observed here are at considerably greater device dimensions compared with those previously reported in Si devices. In terms of future directions, a systematic work comparing different metals for contacts on MoS<sub>2</sub> at sub-K temperatures would be a fascinating study, as there are indications that Sb<sup>44</sup> and Bi<sup>45</sup> contacts hold promise. This would enhance our understanding of whether the contact metals are significant in some of these observed phenomena. Conductive atomic force microscopy may help to identify the physical source of the apparent parallel conduction observed. Moreover, as high-frequency behavior and performance are important factors when considering quantum electron devices, 46-49 future directions for MoS<sub>2</sub> device characterization at cryogenic temperatures should incorporate these aspects. Finally, one must move toward characterizing devices fabricated from thin-film MoS2, rather than flakes, to explore if this physics is still present as we scale up the number of devices in this material system, which is essential in order to develop large-scale integrated circuits. With a large number of

devices fabricated from large-area films, we would be able to build a large enough dataset with which we could develop a suitable model to explain the observed behavior, for example, the unusually large temperature coefficient of the threshold voltage.

# ASSOCIATED CONTENT

# **Supporting Information**

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acsanm.5c04844.

Details of the fabrication process, SEM and AFM images of the devices (Figure S1), transfer characteristics of a p-type  $MoS_2$ -based MOSFET at 0.35 K with the *y*-axis in linear and logarithmic scales (Figure S2), transfer characteristics of an n-type  $MoS_2$ -based MOSFET at low  $V_D$  (0.6 V), with temperature varying from 0.3 to 20 K, with the *y*-axis in logarithmic scale (Figure S3), current—voltage characteristics at 300 K proving the linear regime of the device above  $V_G = 0$  V (Figure S4), current—voltage characteristics at 34 K showing the "diode"-like effect which is absent at room temperature (Figure S5), and subthreshold swing as a function of temperature (Figure S6) (PDF)

## AUTHOR INFORMATION

# **Corresponding Authors**

Michael D. Thompson — Department of Physics, Lancaster University, Lancaster LA1 4YB, U.K.; orcid.org/0000-0002-8551-4806; Email: m.thompson@lancaster.ac.uk

Ray Duffy — Tyndall National Institute, University College Cork, Cork T12 R5CP, Ireland; Email: ray.duffy@tyndall.ie

#### **Authors**

**Matthew Haworth** – Department of Physics, Lancaster University, Lancaster LA1 4YB, U.K.

Owain T. Hughes – Department of Physics, Lancaster University, Lancaster LA1 4YB, U.K.

Jonathan Prance — Department of Physics, Lancaster University, Lancaster LA1 4YB, U.K.; orcid.org/0000-0001-5009-383X

Yuri Pashkin — Department of Physics, Lancaster University, Lancaster LA1 4YB, U.K.; orcid.org/0000-0003-4767-8217

Luca Panarella – Tyndall National Institute, University College Cork, Cork T12 RSCP, Ireland

Farzan Gity — Tyndall National Institute, University College Cork, Cork T12 R5CP, Ireland; orcid.org/0000-0003-3128-1426

Gioele Mirabelli – Tyndall National Institute, University College Cork, Cork T12 R5CP, Ireland

Giorgos Fagas – Tyndall National Institute, University College Cork, Cork T12 R5CP, Ireland

Complete contact information is available at: https://pubs.acs.org/10.1021/acsanm.5c04844

#### **Author Contributions**

Conceptualization (L.P., F.G., G.M., G.F., R.D., M.D.T., Y.A.P.); Data curation (L.P., R.D., M.D.T.); Formal analysis (L.P., F.G., G.M., R.D., M.D.T.); Funding acquisition (G.F., R.D., M.D.T., J.R.P.); Investigation (L.P., F.G., R.D., M.D.T., J.R.P., M.H., O.H.); Methodology (F.G., G.M., G.F., R.D., Y.A.P.); Project administration (G.F., R.D., M.D.T., J.R.P.);

Supervision (G.F., R.D., M.D.T., J.R.P.); Validation (F.G., R.D.); Visualization (M.D.T.); Writing—original draft (R.D.); Writing—review and editing (F.G., G.F., R.D., M.D.T., J.R.P., Y.A.P.).

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

This work was supported by the European Commission through project ASCENT+: Access to European Infrastructure for Nanoelectronics, funded under H2020 (Grant Agreement 871130), and the EU H2020 European Microkelvin Platform (Grant Agreement 824109). M.D.T. acknowledges financial support from the Royal Academy of Engineering (RF \201819\18\2).

# REFERENCES

- (1) Liu, X. L.; Hersam, M. C. 2D materials for quantum information science. *Nat. Rev. Mater.* **2019**, 4 (10), 669–684.

- (2) Polyushkin, D. K.; Wachter, S.; Mennel, L.; Paur, M.; Paliy, M.; Iannaccone, G.; Fiori, G.; Neumaier, D.; Canto, B.; Mueller, T. Analogue two-dimensional semiconductor electronics. *Nat. Electron.* **2020**, 3 (8), 486–491.

- (3) Movva, H. C. P.; Rai, A.; Kang, S.; Kim, K.; Fallahazad, B.; Taniguchi, T.; Watanabe, K.; Tutuc, E.; Banerjee, S. K. High-Mobility Holes in Dual-Gated WSe Field-Effect Transistors. *ACS Nano* **2015**, *9* (10), 10402–10410.

- (4) Chuang, H. J.; Chamlagain, B.; Koehler, M.; Perera, M. M.; Yan, J. Q.; Mandrus, D.; Tománek, D.; Zhou, Z. X. Low-Resistance 2D/2D Ohmic Contacts: A Universal Approach to High-Performance WSe, MoS, and MoSe Transistors. *Nano Lett.* **2016**, *16* (3), 1896–1902.

- (5) Sackville Hamilton, A. C. Electron Transport in Two-Dimensional Molybdenum; Disulphide University College London, 2018.

- (6) Kim, B. K.; Kim, T. H.; Choi, D. H.; Kim, H.; Watanabe, K.; Taniguchi, T.; Rho, H.; Kim, J. J.; Kim, Y. H.; Bae, M. H. Origins of genuine Ohmic van der Waals contact between indium and MoS. *Npj* 2D Mater. Appl. **2021**, 5 (1), 9.

- (7) Gao, Q.; Zhang, C.; Zhang, Z.; Yi, Z.; Pan, X.; Chi, F.; Liu, L.; Li, X.; Wu, Y.High-Frequency Performance of MoS 2 Transistors at Cryogenic Temperatures. In *IEEE 15th International Conference on Solid-State & Integrated Circuit Technology (ICSICT)*; IEEE: Kunming, China, 2020, PP. 1–3. DOI:

- (8) Lau, C. S.; Chee, J. Y.; Ang, Y. S.; Tong, S. W.; Cao, L. M.; Ooi, Z. E.; Wang, T.; Ang, L. K.; Wang, Y.; Chhowalla, M.; et al. Quantum Transport in Two-Dimensional WS with High-Efficiency Carrier Injection through Indium Alloy Contacts. *ACS Nano* **2020**, *14* (10), 13700–13708.

- (9) Sangwan, V. K.; Lee, H. -S.; Bergeron, H.; Balla, I.; Beck, M. E.; Chen, K. -S.; Hersam, M. C. Multi-terminal memtransistors from polycrystalline monolayer molybdenum disulfide. *Nature* **2018**, *554* (7693), 500–504.

- (10) Mirabelli, G.; Schmidt, M.; Sheehan, B.; Cherkaoui, K.; Monaghan, S.; Povey, I.; McCarthy, M.; Bell, A. P.; Nagle, R.; Crupi, F.; et al. Back-gated Nb-doped MoS2 junctionless field-effect-transistors. *AIP Adv.* **2016**, *6* (2), 55.

- (11) Mirabelli, G.; Gity, F.; Monaghan, S.; Hurley, P. K.; Duffy, R.Impact of impurities, interface traps and contacts on MoS MOSFETs: modelling and experiments 2017 47th European Solid-State Device Research Conference (ESSDERC) IEEE Leuven, Belgium 2017288–291

- (12) Mirabelli, G.; Hurley, P. K.; Duffy, R. Physics-based modelling of MoS: the layered structure concept. *Semicond. Sci. Technol.* **2019**, 34 (5), 055015.

- (13) Lee, K.; Kulkarni, G.; Zhong, Z. H. Coulomb blockade in monolayer MoS single electron transistor. *Nanoscale* **2016**, 8 (14), 7755–7760.

- (14) Beckers, A.; Jazaeri, F.; Enz, C. Cryogenic MOS Transistor Model. *IEEE T. Electron Dev.* **2018**, 65 (9), 3617–3625.

- (15) Beckers, A.; Jazaeri, F.; Enz, C. Characterization and Modeling of 28-nm Bulk CMOS Technology Down to 4.2 K. *Ieee J. Electron Dev.* **2018**, *6* (1), 1007–1018.

- (16) Beckers, A.; Jazaeri, F.; Bohuslayskyi, H.; Hutin, L.; De Franceschi, S.; Enz, C. Characterization and modeling of 28-nm FDSOI CMOS technology down to cryogenic temperatures. *Solid-State Electron.* **2019**, *159*, 106–115.

- (17) Bohuslavskyi, H.; Jansen, A. G. M.; Barraud, S.; Barral, V.; Cassé, M.; Le Guevel, L.; Jehl, X.; Hutin, L.; Bertrand, B.; Billiot, G.; et al. Cryogenic Subthreshold Swing Saturation in FD-SOI MOSFETs Described With Band Broadening. *IEEE Electr. Device L* **2019**, *40* (5), 784–787

- (18) Beckers, A.; Jazaeri, F.; Enz, C. Theoretical Limit of Low Temperature Subthreshold Swing in Field-Effect Transistors. *IEEE Electr. Device L* **2020**, *41* (2), 276–279.

- (19) Ghibaudo, G.; Aouad, M.; Casse, M.; Martinie, S.; Poiroux, T.; Balestra, F. On the modelling of temperature dependence of subthreshold swing in MOSFETs down to cryogenic temperature. *Solid State Electron.* **2020**, *170*, 107820.

- (20) Maria, F. S. D.; Contamin, L.; Paz, B. C.; Cassé, M.; Theodorou, C.; Balestra, F.; Ghibaudo, G. Lambert-W function-based parameter extraction for FDSOI MOSFETs down to deep cryogenic temperatures. *Solid-State Electron.* **2021**, *186*, 108175.

- (21) Maria, F. S. D.; Theodorou, C.; Mescot, X.; Balestra, F.; Ghibaudo, G.; Cassé, M.Low temperature behavior of FD-SOI MOSFETs from micro- to nano-meter channel lengths. In2021 IEEE 14th Workshop on Low Temperature Electronics (WOLTE); IEEE: Matera, Italy, 2021, DOI:

- (22) Balestra, F. S. D.; Contamin, L.; Casse, M.; Theodorou, C.; Balestra, F.; Ghibaudo, G. Comprehensive Kubo-Greenwood modelling of FDSOI MOS devices down to deep cryogenic temperatures. *Solid-State Electron.* **2022**, *192*, 108271.

- (23) Paz, B. C.; Le Guevel, L.; Cassé, M.; Billiot, G.; Pillonnet, G.; Jansen, A. G. M.; Maurand, R.; Haendler, S.; Juge, A.; Vincent, E., et al.. Variability Evaluation of 28nm FD-SOI Technology at Cryogenic Temperatures down to 100mK for Quantum Computing. In 2020 IEEE Symposium on VLSI Technology; IEEE: Honolulu, HI, USA 2020.

- (24) Han, H. C.; Jazaeri, F.; D'Amico, A.; Zhao, Z. X.; Lehmann, S.; Kretzschmar, C.; Charbon, E.; Enz, C. In-depth Cryogenic Characterization of 22 nm FDSOI Technology for Quantum Computation. In 2021 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EuroSOI-ULIS); IEEE: Caen, France, 2021. DOI:

- (25) Cherkaoui, K.; La Torraca, P.; Lin, J.; Maraviglia, N.; Andersen, A.; Wernersson, L. E.; Padovani, A.; Larcher, L.; Hurley, P. K.. High-k/InGaAs interface defects at cryogenic temperature; Solid State Electron; Elsevier 2023, Vol. 207.

- (26) Xue, J. H.; Huang, S. Y.; Wang, J. Y.; Xu, H. Q. Mott variable-range hopping transport in a MoS nanoflake. *RSC Adv.* **2019**, 9 (31), 17885–17890.

- (27) He, G.; Ghosh, K.; Singisetti, U.; Ramamoorthy, H.; Somphonsane, R.; Bohra, G.; Matsunaga, M.; Higuchi, A.; Aoki, N.; Najmaei, S.; et al. Conduction Mechanisms in CVD-Grown Monolayer MoS Transistors: From Variable-Range Hopping to Velocity Saturation. *Nano Lett.* **2015**, *15* (8), 5052–5058.

- (28) Peng, S.; Jin, Z.; Yao, Y.; Li, L.; Zhang, D.; Shi, J.; Huang, X.; Niu, J.; Zhang, Y.; Yu, G. Metal-Contact-Induced Transition of Electrical Transport in Monolayer MoS 2: From Thermally Activated to Variable-Range Hopping. *Adv. Electron. Mater.* **2019**, 5 (7), 1900042.

- (29) Grillo, A.; Di Bartolomeo, A.; Urban, F.; Passacantando, M.; Caridad, J. M.; Sun, J. B.; Camilli, L. Observation of 2D Conduction in Ultrathin Germanium Arsenide Field-Effect Transistors. *ACS Appl. Mater. Interfaces* **2020**, *12* (11), 12998–13004.

- (30) Pollak, M.; Shklovskiĭ, B. I. Hopping transport in solids; North-Holland; Sole distributors for the USA and Canada; Elsevier, 1991.

- (31) Papadopoulos, N.; Steele, G. A.; van der Zant, H. S. J. Efros-Shklovskii variable range hopping and nonlinear transport in 1T/1T'-MoS. *Phys. Rev. B* **2017**, *96* (23), 63.

- (32) Ghatak, S.; Pal, A. N.; Ghosh, A. Nature of Electronic States in Atomically Thin MoS Field-Effect Transistors. *ACS Nano* **2011**, 5 (10), 7707–7712.

- (33) Shklovskii, B. I.; Efros, A. L. Electronic properties of doped semiconductors; Springer, 1984.

- (34) Coleman, E.; Monaghan, S.; Gity, F.; Mirabelli, G.; Duffy, R.; Sheehan, B.; Balasubramanyam, S.; Bol, A. A.; Hurley, P. Scrutinizing pre- and post-device fabrication properties of atomic layer deposition WS thin films. *Appl. Phys. Lett.* **2023**, *123* (1), *23*.

- (35) Duffy, R.; Foley, P.; Filippone, B.; Mirabelli, G.; O'Connell, D.; Sheehan, B.; Carolan, P.; Schmidt, M.; Cherkaoui, K.; Gatensby, R.; et al. Structural and Electrical Investigation of MoS Thin Films Formed by Thermal Assisted Conversion of Mo Metal. *Ecs J. Solid State Sci.* **2016**, *5* (11), Q3016–Q3020.

- (36) Tzou, J. J.; Yao, C. C.; Cheung, R.; Chan, H. The Temperature-Dependence of Threshold Voltages in Submicrometer Cmos. *IEEE Electr. Device L* **1985**, 6 (5), 250–252.

- (37) Klaassen, F. M.; Hes, W. On the Temperature-Coefficient of the Mosfet Threshold Voltage. *Solid-State Electron* **1986**, 29 (8), 787–789

- (38) d'Alessandro, V.; Spirito, P. Achieving accuracy in modeling the temperature coefficient of threshold voltage in MOS transistors with uniform and horizontally nonuniform channel doping. *Solid-State Electron* **2005**, 49 (7), 1098–1106.

- (39) Nishida, Y.; Eikyu, K.; Shimizu, A.; Yamashita, T.; Oda, H.; Inoue, Y.; Shibahara, K. Temperature Coefficient of Threshold Voltage in High-k Metal Gate Transistors with Various TiN and Capping Layer Thicknesses. *Jpn. J. Appl. Phys.* **2010**, 49 (4S), 04DC03.

- (40) Chien, Y.-C.; Feng, X.; Chen, L.; Chang, K.-C.; Tan, W. C.; Li, S.; Huang, L.; Ang, K.-W. Charge Carrier Mobility and Series Resistance Extraction in 2D Field-Effect Transistors: Toward the Universal Technique. *Adv. Funct. Mater.* **2021**, *31* (41), 2105003.

- (41) Yu, P. Y.; Cardona, M. Fundamentals of semiconductors: physics and materials properties; Springer, 2010.

- (42) Addou, R.; McDonnell, S.; Barrera, D.; Guo, Z. B.; Azcatl, A.; Wang, J.; Zhu, H.; Hinkle, C. L.; Quevedo-Lopez, M.; Alshareef, H. N.; et al. Impurities and Electronic Property Variations of Natural MoS2 Crystal Surfaces. *ACS Nano* **2015**, *9* (9), 9124–9133.

- (43) Catapano, E.; Frutuoso, T. M.; Cassé, M.; Ghibaudo, G. On the Zero Temperature Coefficient in Cryogenic FD-SOI MOSFETs. *IEEE T. Electron Dev.* **2023**, *70* (3), 845–849.

- (44) Li, W. S.; Gong, X. S.; Yu, Z. H.; Ma, L.; Sun, W. J.; Gao, S.; Köroglu, Ç.; Wang, W. F.; Liu, L.; Li, T. T.; Ning, H.; et al. Approaching the quantum limit in two-dimensional semiconductor contacts. *Nature* **2023**, *613* (7943), 274–279.

- (45) Shen, P. -C.; Su, C.; Lin, Y. X.; Chou, A. -S.; Cheng, C. -C.; Park, J. -H.; Chiu, M. -H.; Lu, A. -Y.; Tang, H. -L.; Tavakoli, M. -M.; et al. Ultralow contact resistance between semimetal and monolayer semiconductors. *Nature* **2021**, *593* (7858), 211–217.

- (46) Gao, Q. G.; Zhang, C. F.; Liu, P.; Hu, Y. F.; Yang, K. Q.; Yi, Z. C. A.; Liu, L. M.; Pan, X. J.; Zhang, Z.; Yang, J. J.; et al. Effect of Back-Gate Voltage on the High-Frequency Performance of Dual-Gate MoS Transistors. *Nanomaterials-Basel.* **2021**, *11* (6), 1594.

- (47) Gao, Q. G.; Zhang, C. F.; Yang, K. Q.; Pan, X. J.; Zhang, Z.; Yang, J. J.; Yi, Z. C.; Chi, F.; Liu, L. M. High-Performance CVD Bilayer MoS Radio Frequency Transistors and Gigahertz Mixers for Flexible Nanoelectronics. *Micromachines-Basel* **2021**, *12* (4), 451.

- (48) Kim, Y. S.; Ducournau, G.; Skrzypczak, S.; Yang, S. J.; Szriftgiser, P.; Wainstein, N.; Stern, K.; Happy, H.; Yalon, E.; Pallecchi, E.; et al. Monolayer molybdenum disulfide switches for 6G communication systems. *Nat. Electron.* **2022**, *5* (6), 367–373.

- (49) Gao, Q. G.; Lin, D. X.; Xu, S. Y.; Chen, Y. K.; Li, J. B.; Cao, T. F.; Chen, S. M.; Huang, W. Y.; Liu, P.; Zhang, C. F. Performance optimization of nanometer-thin indium-tin oxide transistors by two-step air annealing. *Phys. B* **2023**, *667*, 415188.